CS207 Chapter A

Chapter A 计数器 Counter

计数器 Counter

计数器是最简单的顺序网络类型之一。一个计数器通常由一个或多个触发器构成,这些触发器在收到输入脉冲时按规定的顺序改变状态。

由于时钟脉冲是以已知的时间间隔发生的,所以计数器可以用作测量时间的仪器,从而测量频率的周期。

- 异步和同步计数器。

- 单模和多模计数器。

- 模数计数器。

异步计数器 Aynschronous counters

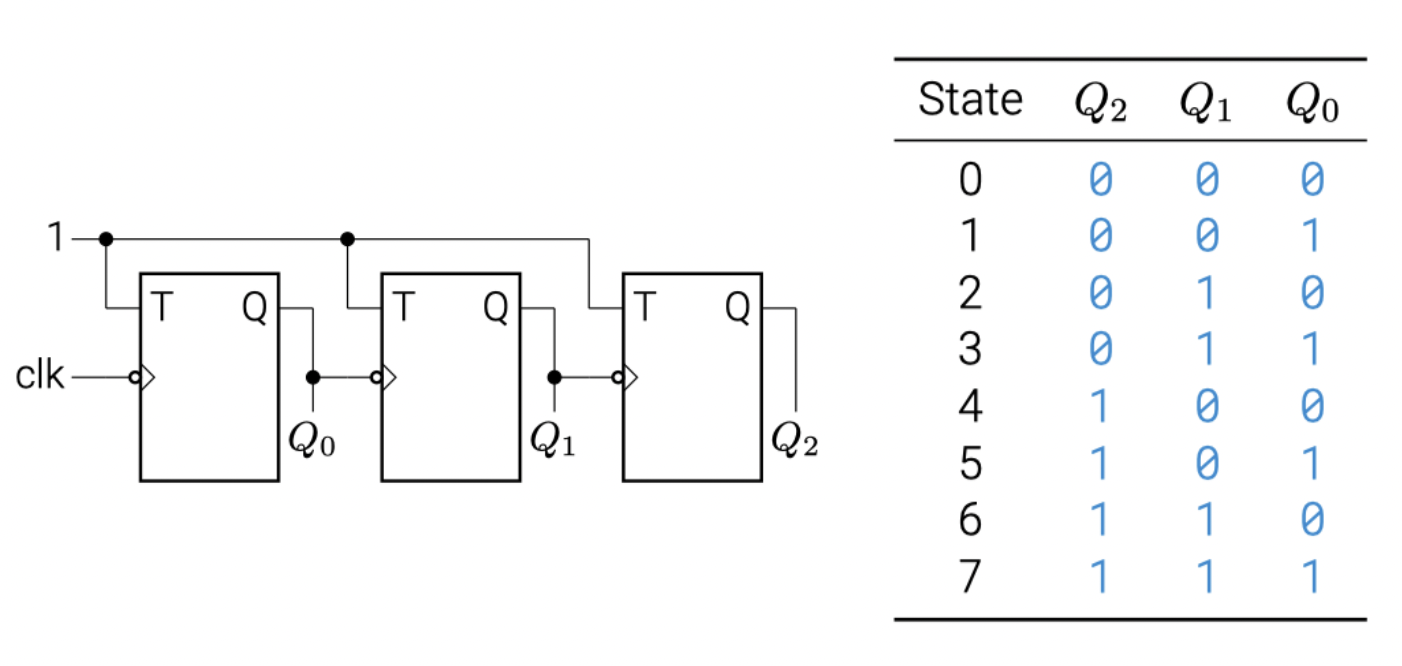

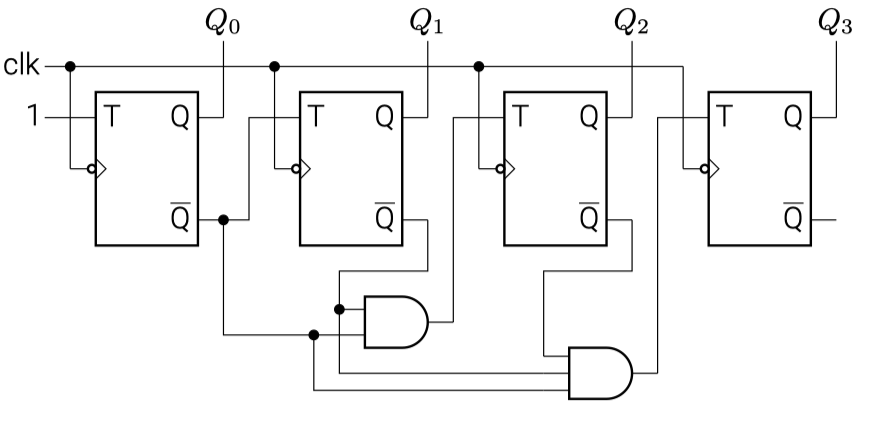

三个触发器的时钟输入以级联方式连接。每个触发器的T输入端连接到一个常数1,这意味着触发器的状态将在其时钟的每个负边沿切换(反向)。

我们假设这个电路的目的是计算主输入CLK(时钟)上出现的脉冲数。因此,第一个触发器的时钟输入被连接到CLK线。

该计数器有8种不同的状态。它是一个MOD-8异步计数器。计数器的模数(或MOD数)是指它在每个完整周期中经过的独特状态的总数。该计数器可以计算的最大二进制数是2 n -1。

输入由一串频率为f的脉冲组成。只有当时钟从1过渡到0时,$Q_0$才会改变。两个输入脉冲将导致$Q_0$的一个脉冲。

$Q_0$的频率为$f/2$,同样地,$Q_1$信号的频率将是$Q_0$信号的一半,即$f/4$,$Q_2$信号的频率$Q_1$信号的一半,即$f/8$。

分频器 Frequency divider

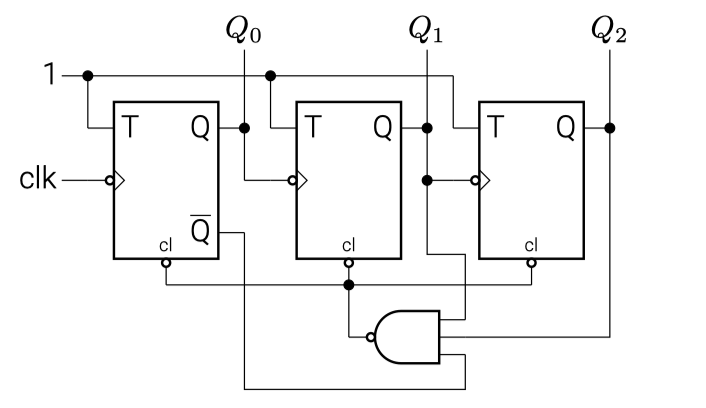

如果电路中使用了n个触发器,那么频率将被$2^n$划分而在实际使用中,我们会经常需要小于$2^n$的频率,这时候就可以跳过一部分频率(识别到特定序列后清零等操作),如下图就是一个MOD-6 计数器,在识别到110后清零三个计数器

- 要构建任何MOD-N计数器,需要遵循以下一般步骤。

- 使用公式$2^n-1<N<2^n$,找出所需MOD-N数字的触发器数量$n$。

- 然后将所有的$n$个触发器连接成一个纹波计数器。

- 找到$N$的二进制数。

- 将所有的触发器输出(当计数为$N$时,$Q=1$,以及$Q′=1$)作为NAND门的输入。

- 将NAND门的输出连接到每个触发器的清零输入。

- 当计数器达到第$N$个状态时,NAND门的输出为低电平,将所有触发器复位为0。

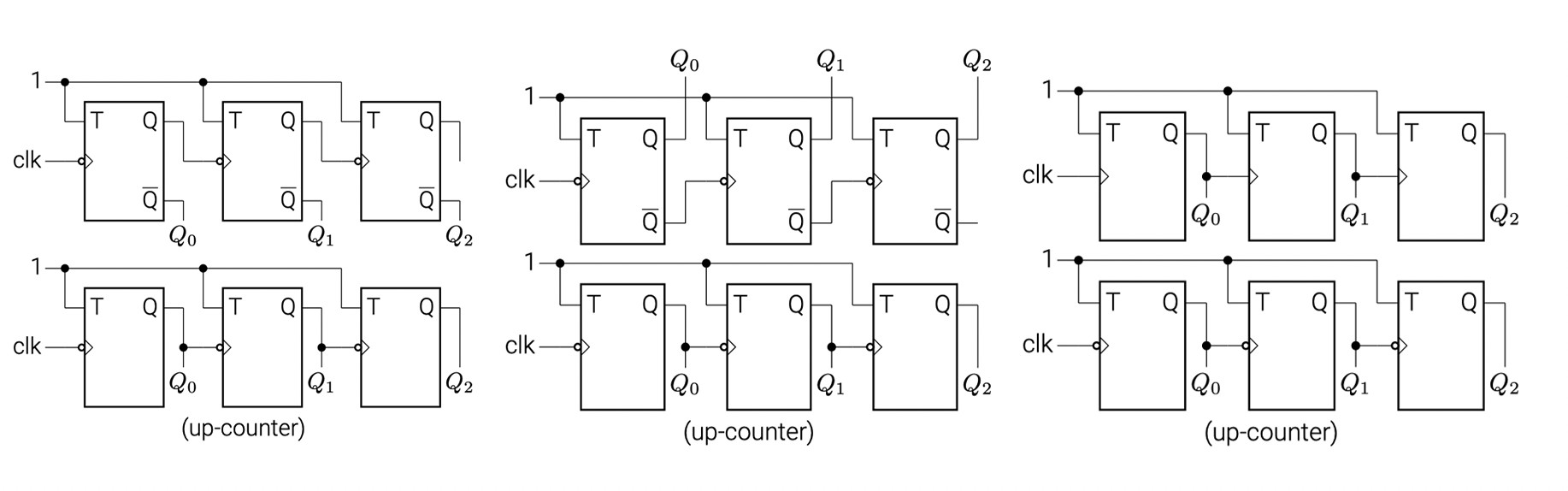

异步下行计数器 Asynchronous up-down counter

一个使用$n$个触发器的下位计数器从$2^n -1$的最大计数开始向下计数到零。

这样的下位机可以用以下三种不同的方式设计。

异步多模计数器 Asynchronous Multimode counter

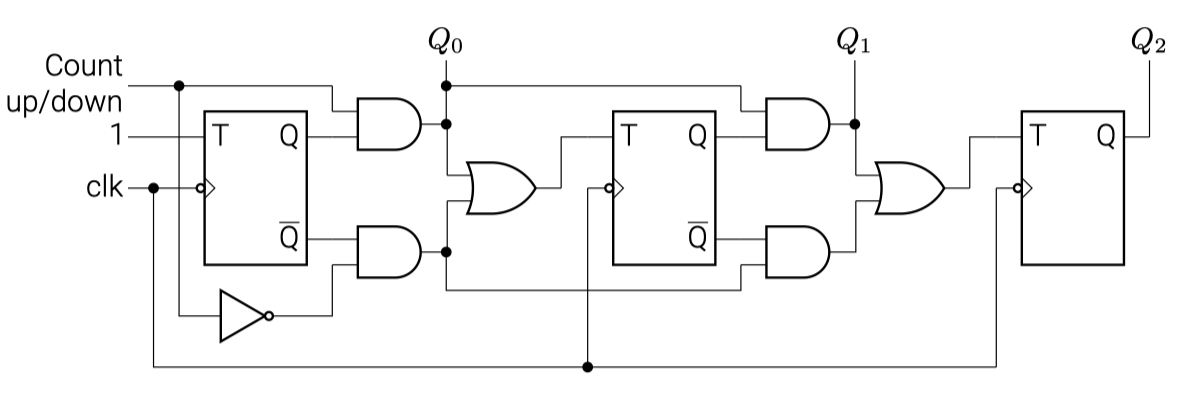

我们已经分别考虑了上算器和下算器,但这两个单元可以结合在一个单一的上-下计数器中。

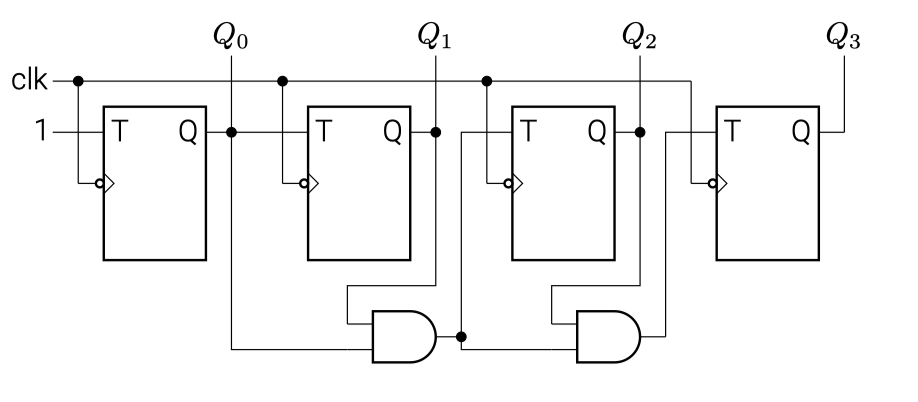

同步计数器 Synchronous counters

所有的触发器都是同步时钟, 随着级数的增加,AND门的数量也在增加,同时每个AND门的输入数也在增加

同步下行计数器 Synchronous down-counter

同步多模计数器 Synchronous Multimode counter

设计一个同步计数器

按照某些一般步骤,可以设计出任何给定计数序列和模数的同步计数器。这些步骤列举如下

根据给定的问题文字描述,画出描述计数器操作的状态图

从状态图中,以表格的形式写出计数序列

找出所需的触发器的数量

决定用于计数器设计的触发器的类型。然后利用触发器的激励表确定从当前状态到所需的下一个状态必须存在的触发器输入

为每个触发器的输入准备K图,以触发器的输出作为输入变量。简化K图,得到最小化的表达式

使用与最小化表达式相对应的触发器和其他门来连接电路

锁定 Lock out

- 在模数小于$2^n$的计数器中,可能会发生计数器偶然发现自己处于任何一个未使用的状态中

- 如果计数器偶然进入这些未使用的状态中的任何一个,它的下一个状态将不为人所知,可能的情况是,计数器从一个未使用的状态到另一个未使用的状态,永远不会到达一个使用的状态。

- 为了防止锁死的发生,我们将每个未使用状态的下一个状态设置为使用的初始状态