CS207 Chapter 9

Chapter 9 寄存器 Register

寄存器 Register

一组触发器,每个触发器共享一个共同的时钟,能够存储一个比特的信息。一个n位的寄存器由一组n个触发器组成,能够存储n位的二进制信息。除了触发器之外,寄存器还可以有组合门来执行某些数据处理任务。

有各种类型的寄存器可供选择。

寄存器 Register

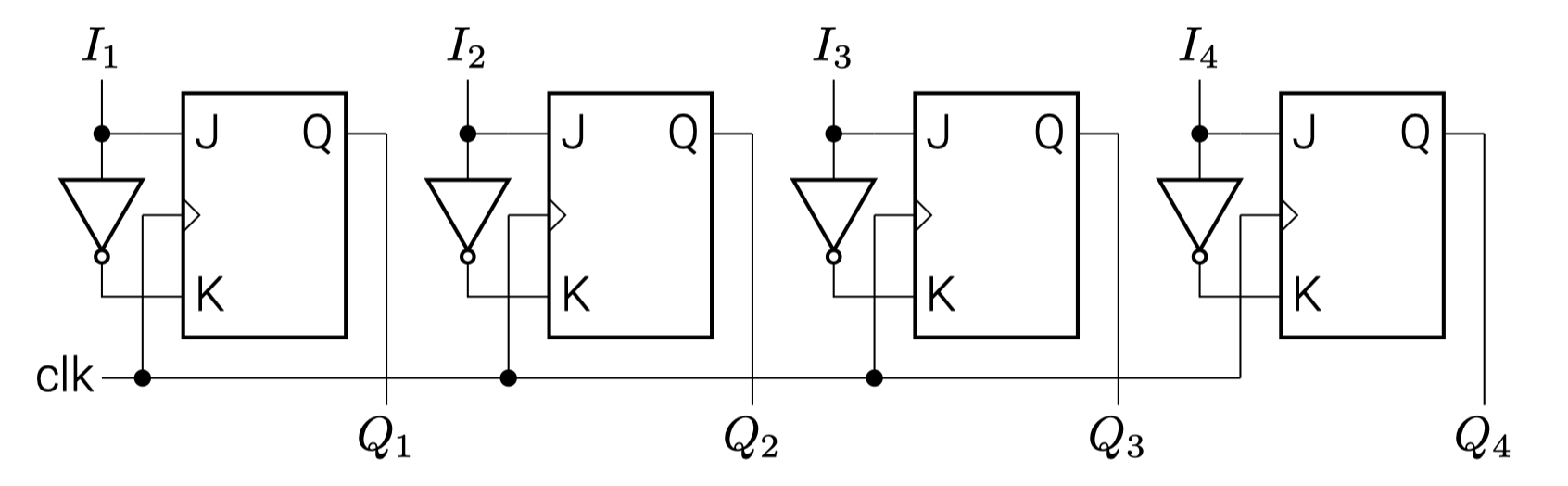

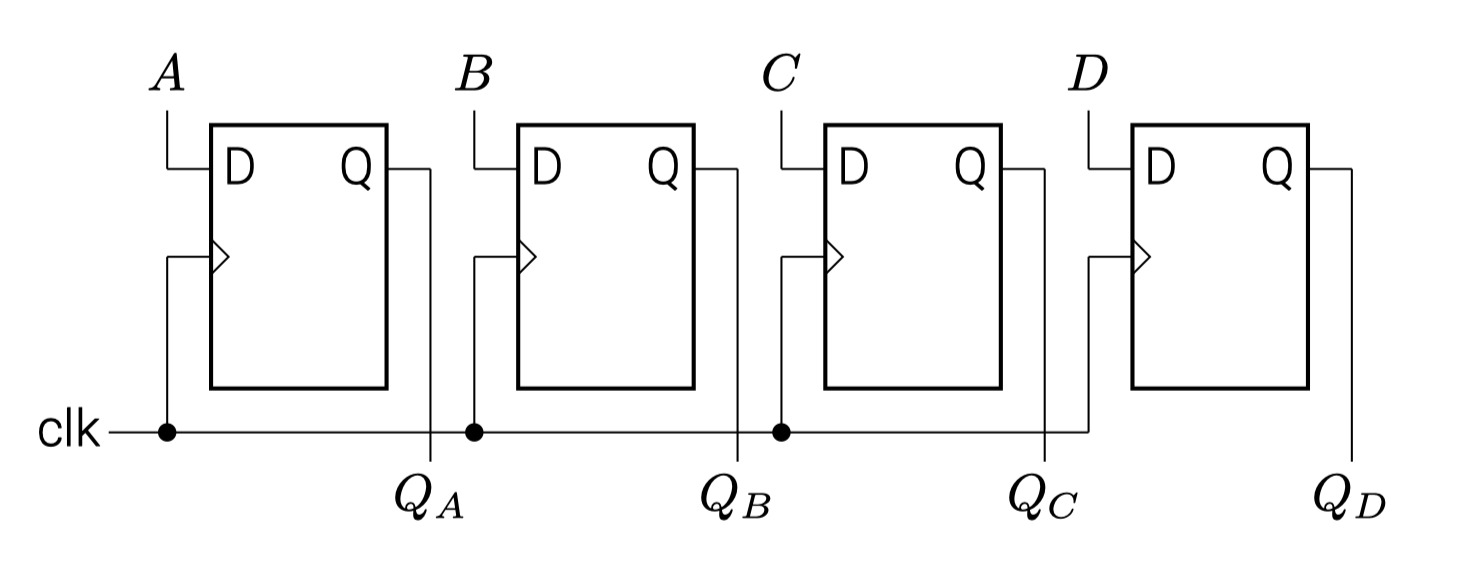

简单寄存器 Simple Register

时钟脉冲在同一时刻启用所有的触发器,这样四个输入端的信息就可以被转移到4位寄存器中。寄存器中的所有触发器都应响应时钟脉冲的转换。

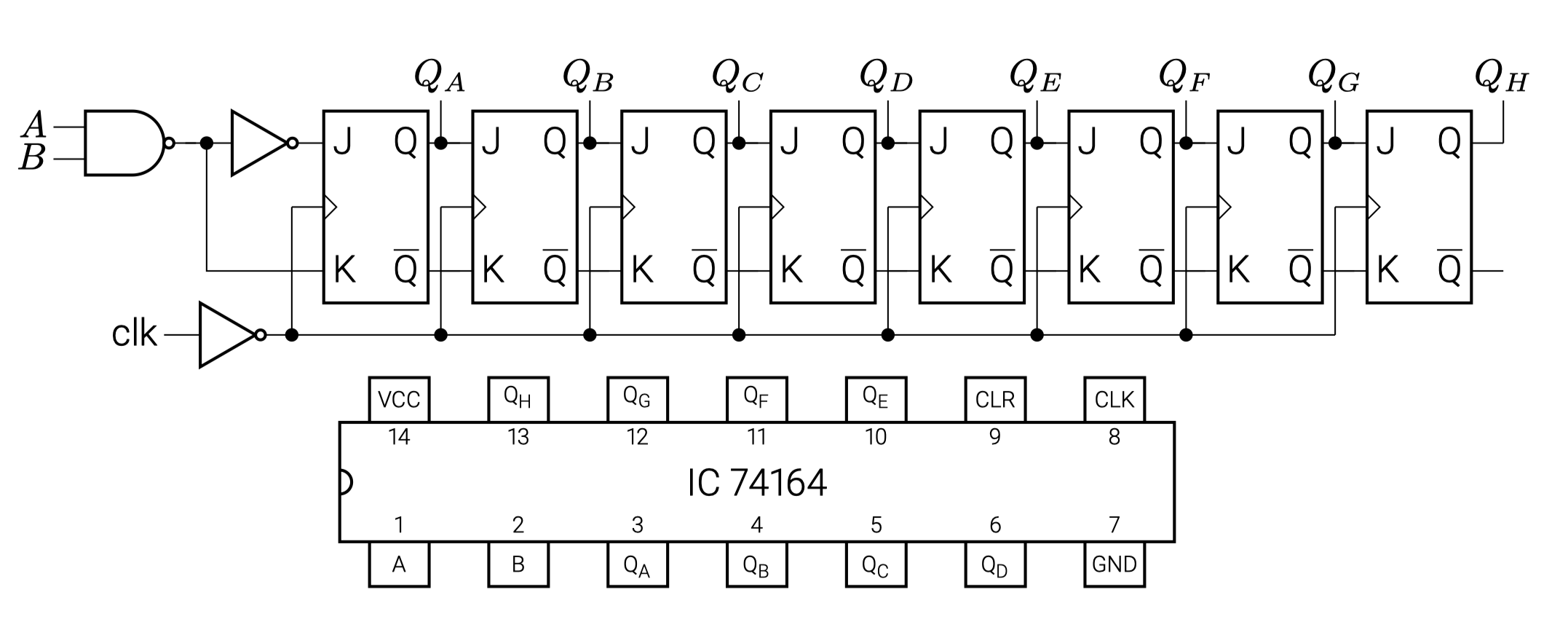

移位寄存器 Shift Register

一个能够将其二进制内容向左或向右移动的寄存器被称为移位寄存器。

- 移位寄存器允许存储的数据从一个特定的位置移动到寄存器中的其他位置。

移位寄存器中的数据可以通过两种方式进行移位。

- 串行移位以串行方式在每个时钟脉冲中一次移位一个比特,从LSB或MSB开始,和

并行移位在一个时钟脉冲中同时移位所有的数据(输入或输出)

- 并行移位操作比串行移位操作快得多。

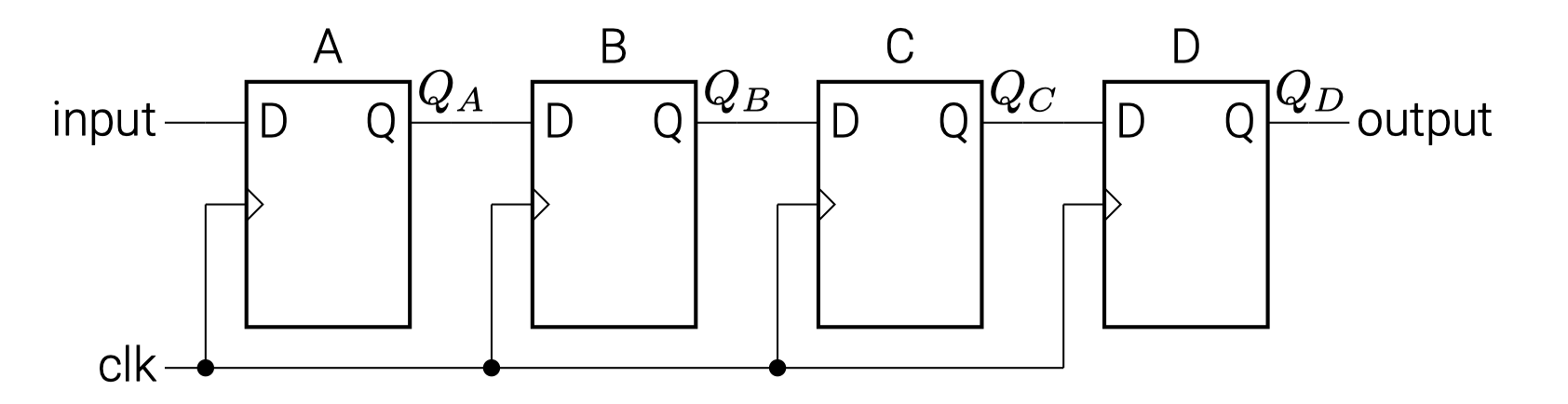

移位寄存器在单条输入线上一次接受一个比特。输出也是以串行方式在单条输出线上获得。寄存器内的数据可以用移位右寄存器从左到右移位,也可以用移位左寄存器从右到左移位。

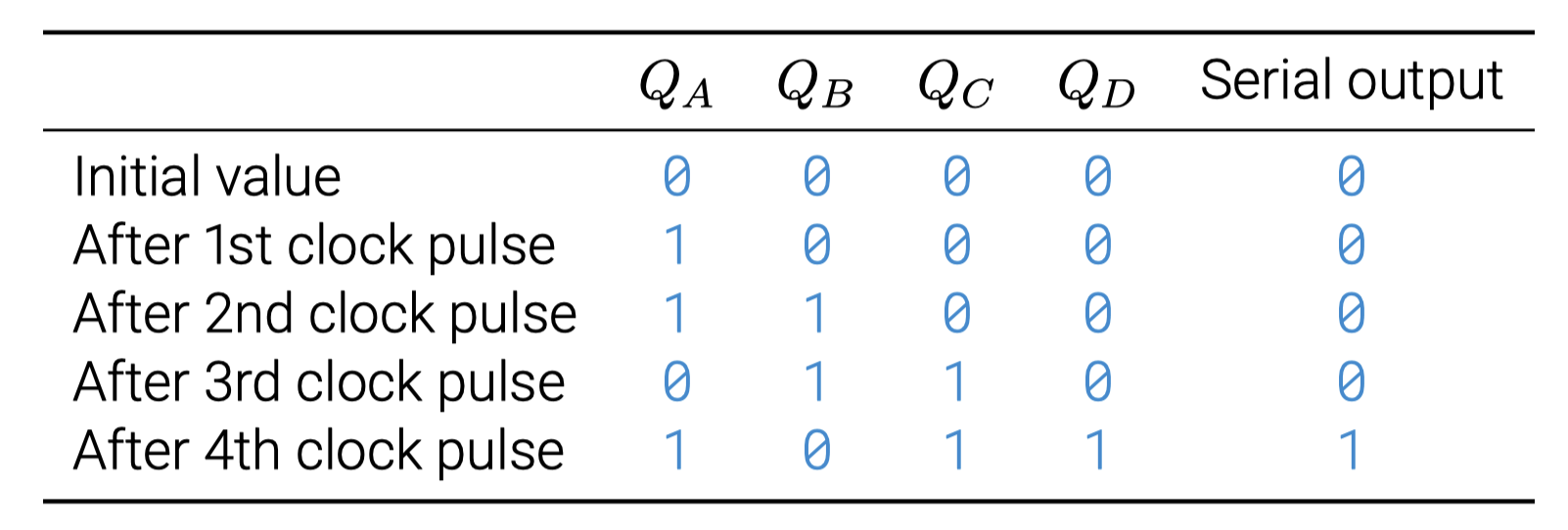

每一个时钟脉冲下,新的数据从A进入,旧数据向右位移,末端数据从$Q_D$输出。例如输入1011进入寄存器:

串入串出寄存器 Serial-in parallel-out register

串入并出寄存器 Serial-in parallel-out register

在这种类型的寄存器中,数据以串行方式移入,但以并行方式移出。

- 为了获得并行的输出数据,需要所有的输出位在同一时间可用。

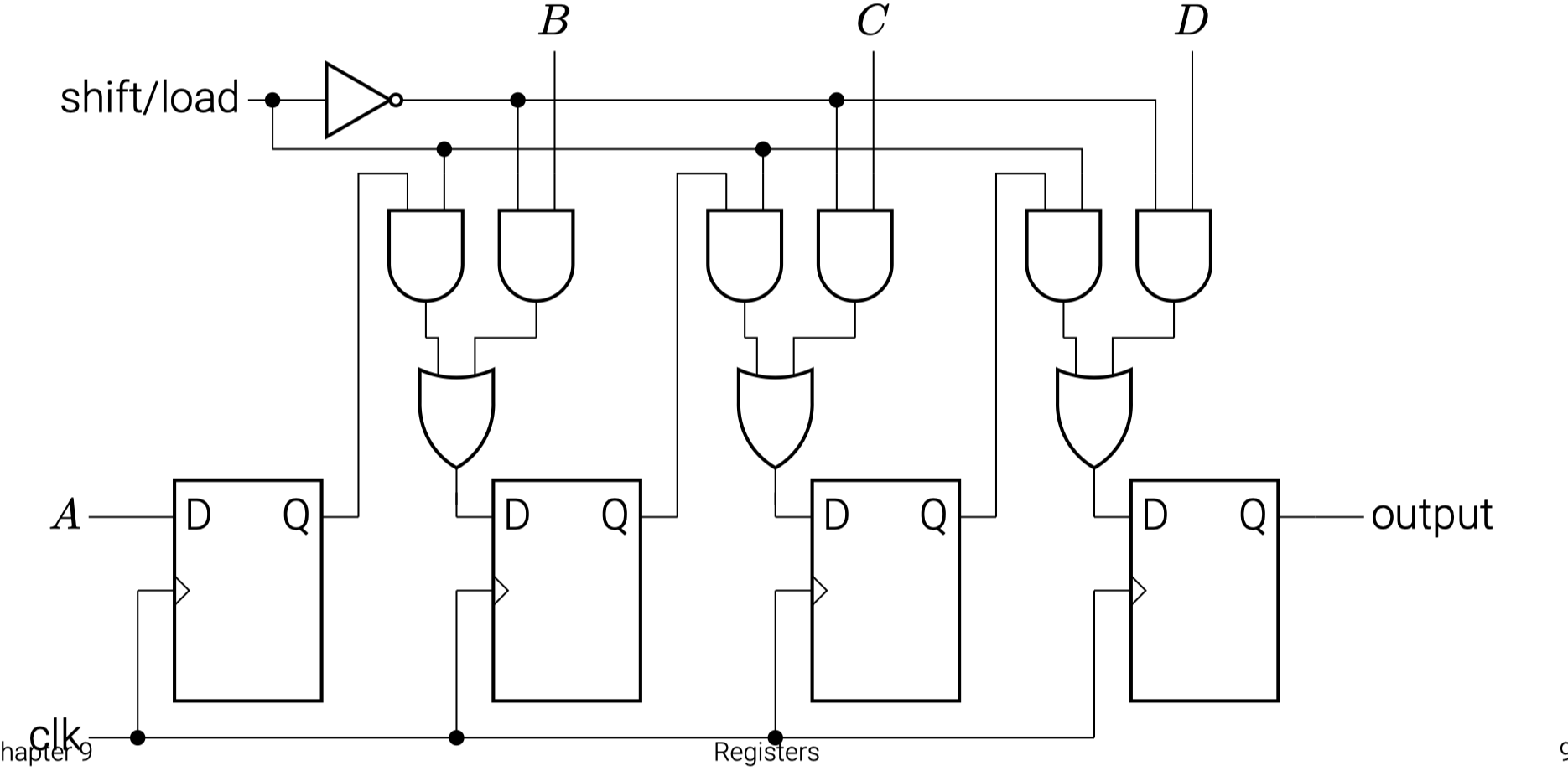

并入串出寄存器 Parallel-in serial-out register

在前面两种情况下,数据是以串行方式移入寄存器的。现在我们可以开发一个想法,将数据平行输入到寄存器中。

并入并出寄存器 Parallel-in parallel-out register

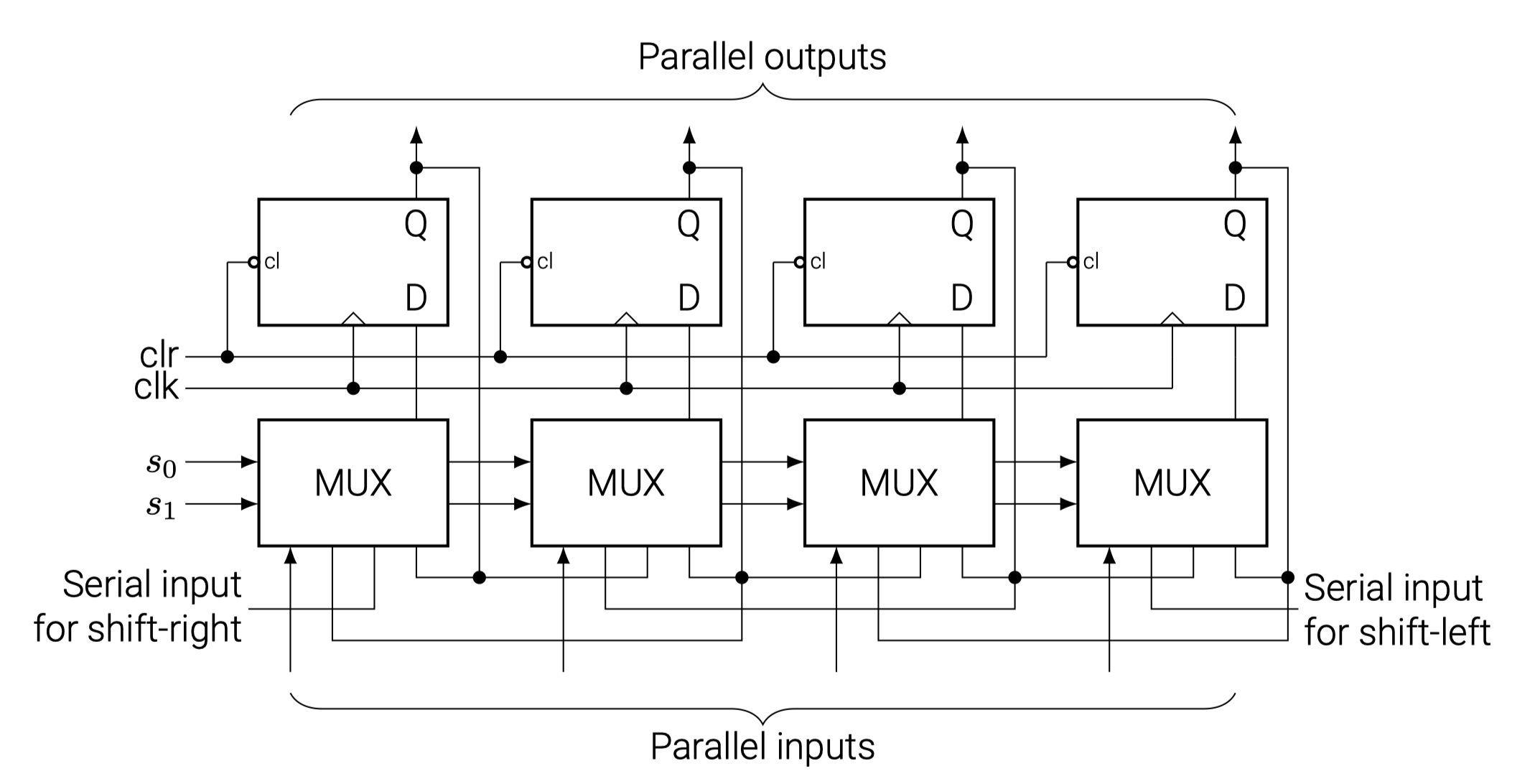

通用移位寄存器 Universal shift register

- 如果一个移位寄存器的触发器输出是可访问的,那么通过移位串行输入的信息可以从触发器的输出中平行取出来。如果在移位寄存器中加入了并行负载能力,那么通过移位存储在寄存器中的数据,就可以将并行输入的数据以串行方式取出。

- 一些移位寄存器为并行传输提供了必要的输入和输出终端。

- 它们也可能同时具有右移和左移的能力。

输入/输出

- 一个清除控制,将寄存器清除为0。

一个时钟输入,用于同步操作。

一个右移控制,用于启用右移操作和与右移相关的串行输入和输出线。

左移控制,启用左移操作和与左移相关的串行输入和输出线。

并行负载控制,用于启用并行传输和与并行传输相关的n条输入线。

n条并行输出线。

- 一个控制状态,使寄存器中的信息在响应时钟的情况下保持不变。

结构

移位寄存器可以被安排成不同类型的计数器。这些移位寄存器使用反馈,其中移位寄存器中最后一个触发器的输出被反馈到第一个触发器。根据这种反馈连接的类型,移位寄存器的计数器被分类为

环形计数器,和

扭曲环或约翰逊或移位计数器。

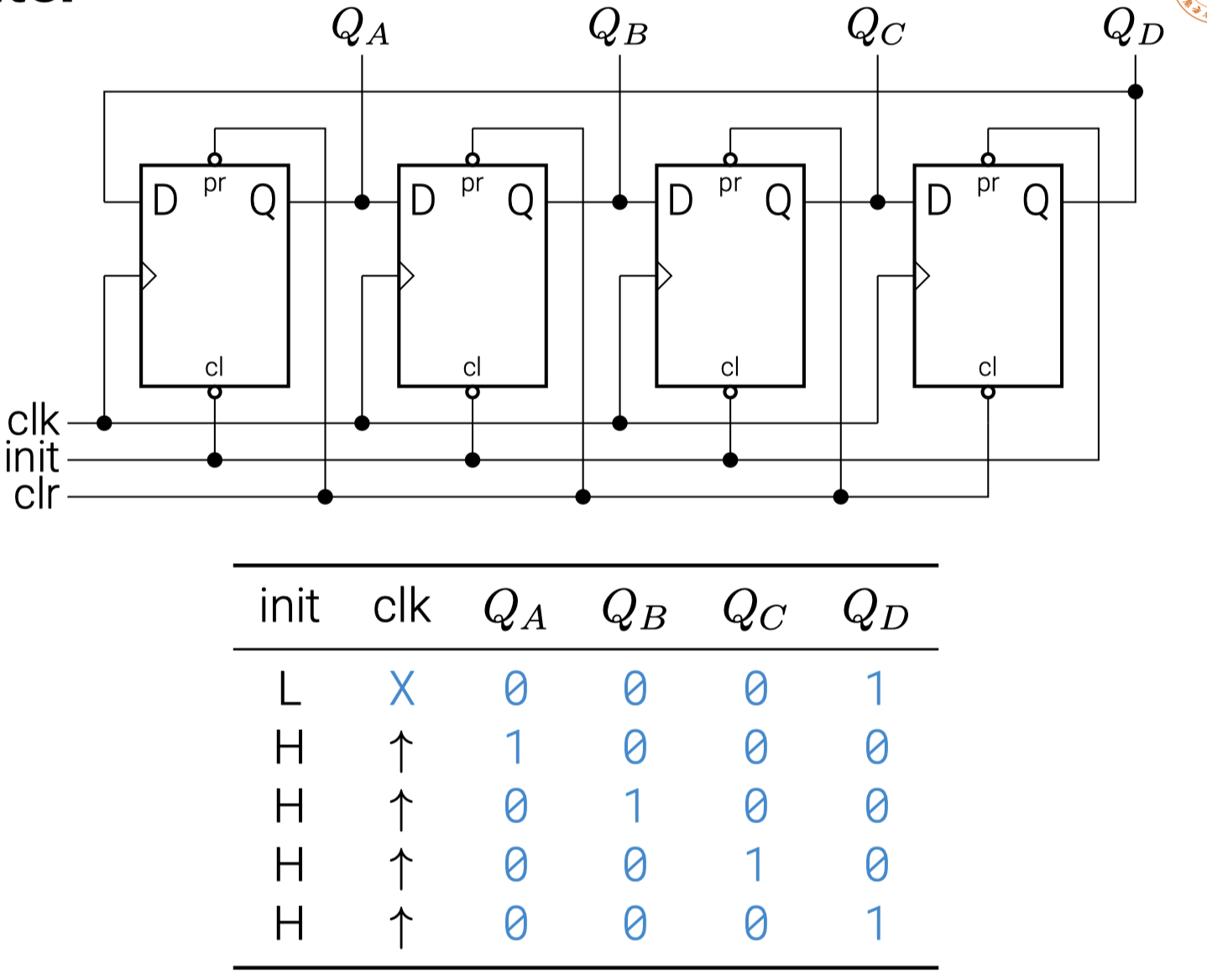

环形计数器 Ring Counter

环形计数器是一个环形移位寄存器,在任何特定时间只有一个触发器被设置,其他的都被清零。单一比特从一个触发器移到另一个触发器,以产生一系列的定时信号。

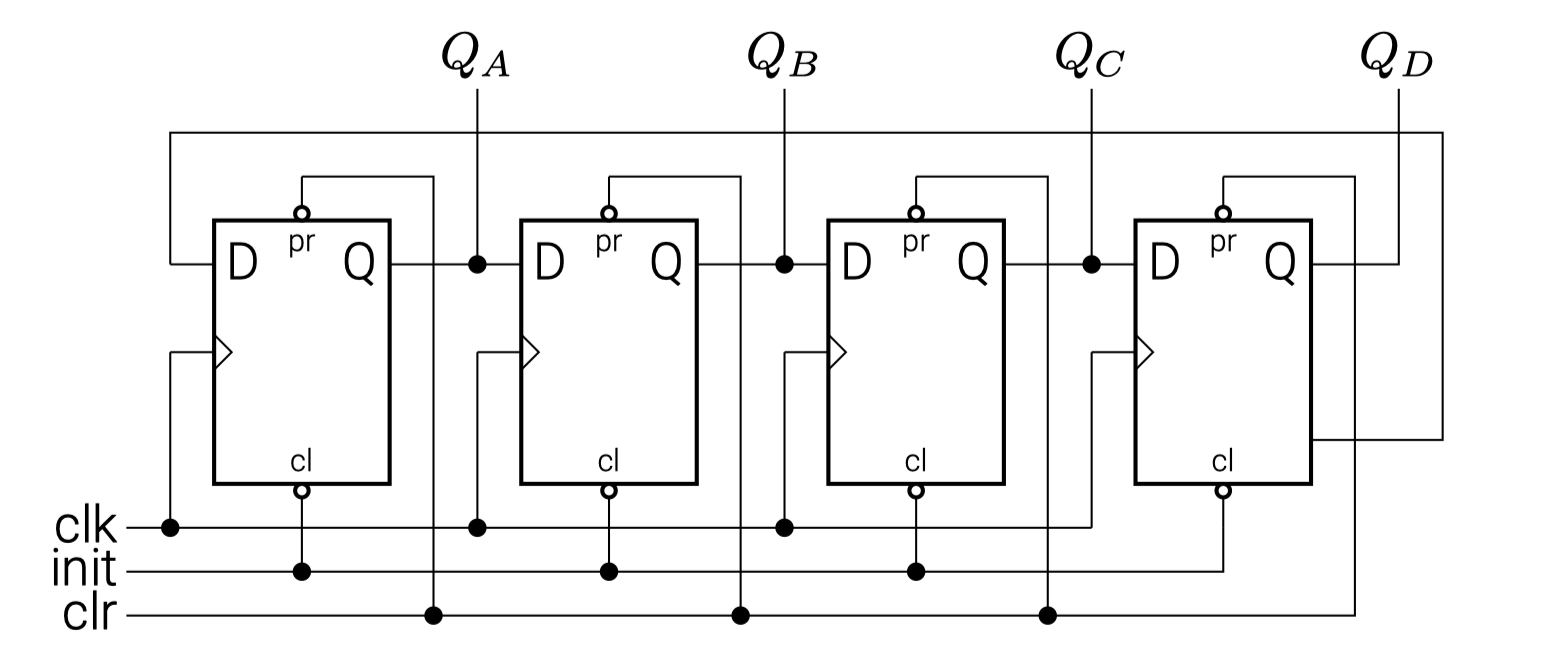

约翰逊计数器 Johnson Counter

一个k位环形计数器在触发器之间循环一个位,以提供k个可区分的状态。

如果移位寄存器被连接成一个开关尾部的环形计数器,那么状态的数量可以增加一倍。

一个循环移位寄存器,最后一个触发器的补码与第一个触发器的输入相连。

该电路的一个缺点是,如果它发现自己处于一个未使用的状态,它将坚持从一个无效的状态转到另一个无效的状态,而永远找不到通往有效状态的路。这个困难可以通过修改电路来纠正,以避免这种不理想的状况。

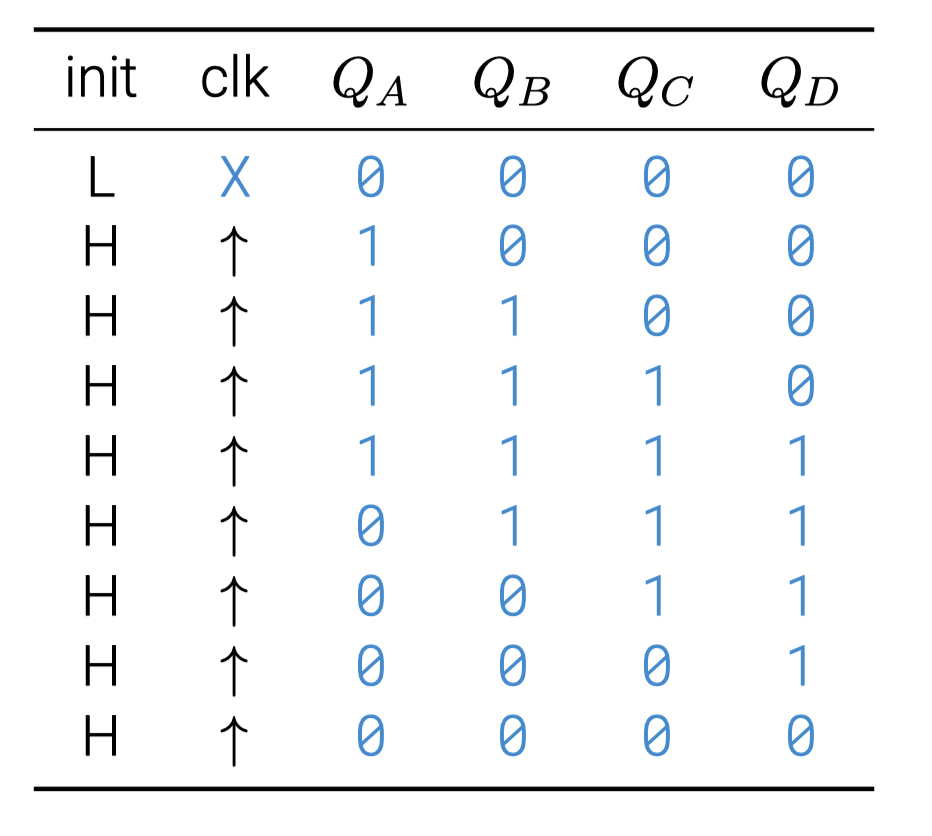

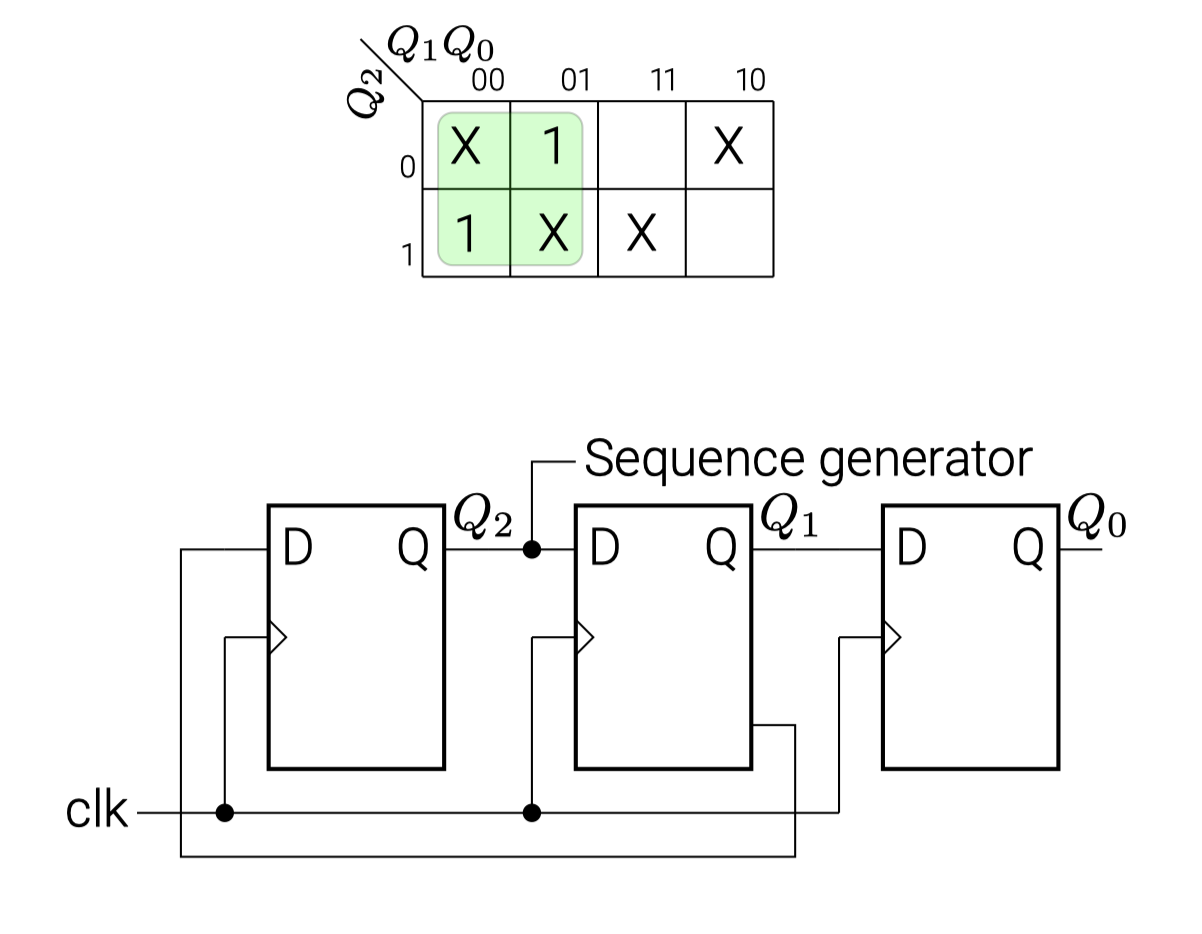

序列发生器 Sequence generator

序列发生器是一个与时钟同步生成所需比特序列的电路。可作为随机位发生器、编码发生器和规定周期发生器使用。

下一个状态解码器的输出是移位寄存器状态的一个函数

- 并连接到移位寄存器的串行输入,这个序列发生器类似于一个环形计数器或一个约翰逊计数器。

产生一个长度为N的序列所需的最小触发器的数量为$N ≤ 2n -1$,我们以构建1001举例

$Q_1$是$Q_2$下移,$Q_0$是$Q_1$下移$Z$是$Q_2$,这样产生的序列就是所需要的序列。然后根据卡诺图化简得到Z的表达式,连接即可

- 当出现两个相同Q组合对应不同的Z时,增加FF的数量即可

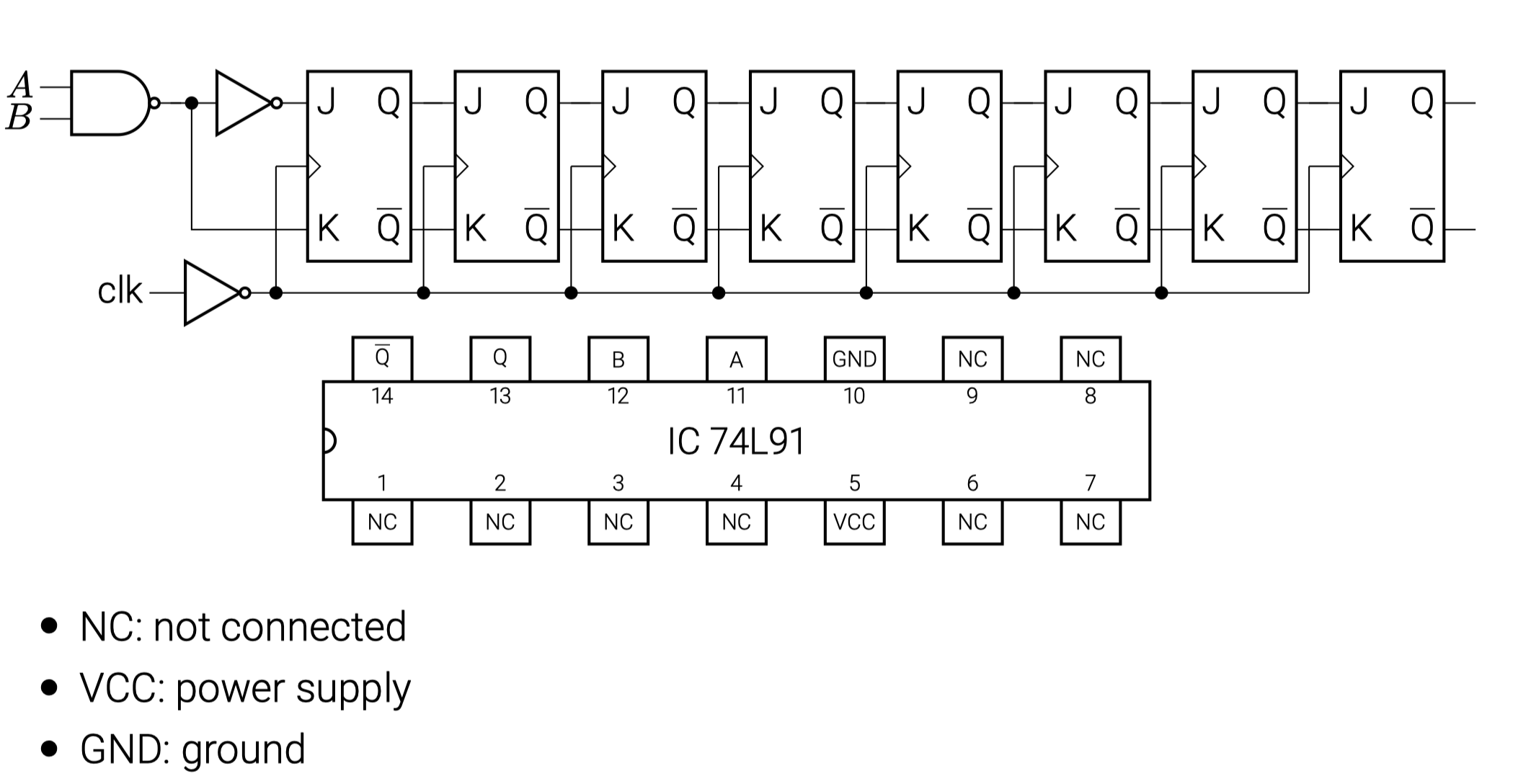

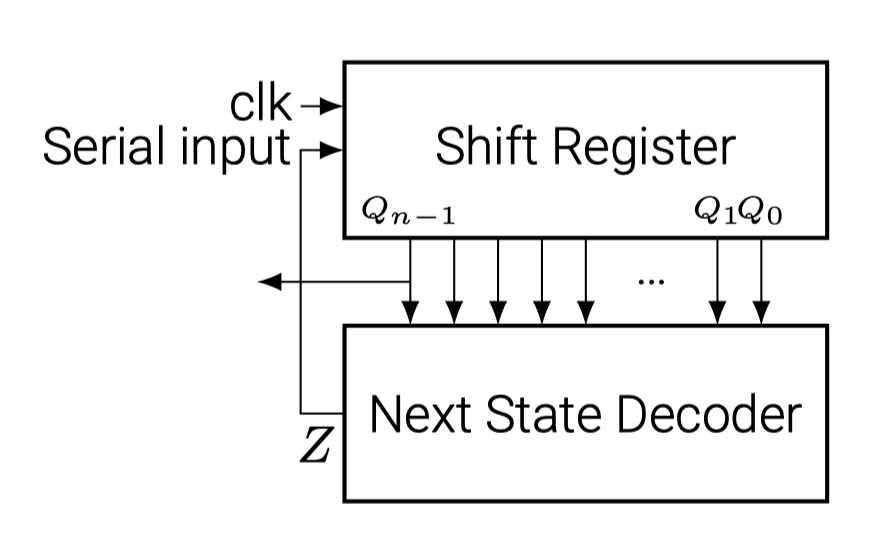

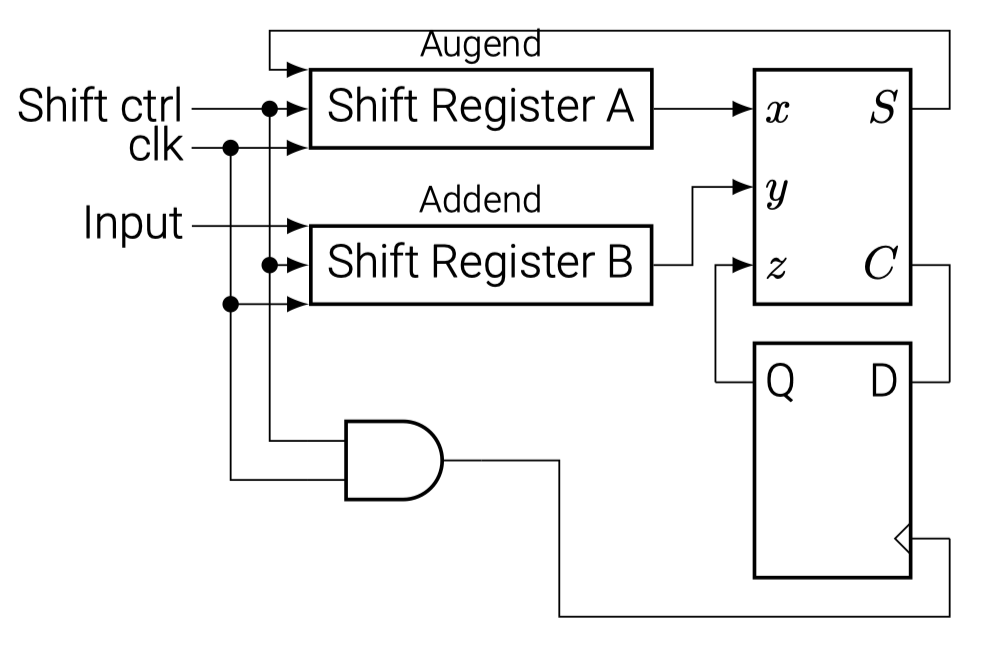

串行加法 Serial addition

要串行添加的两个二进制数字被存储在两个移位寄存器中。

从小的一对bit开始,该电路通过一个全加器(FA)电路一次增加一对比特,全加器的进位被转移到一个D触发器,其输出被用作下一对有效位的结转输入。

最初,寄存器A存储被加数,寄存器B保持加数,进位触发器被清空为0。

A和B的输出为全加器的x和y提供一对有效位。

触发器的输出Q提供了z处的输入进位。

在下一个时钟脉冲中,两个寄存器都向右移动一次,S的和位进入A的最左边的触发器,输出的进位被转移到触发器Q

重复上述过程,直到Shift控制被禁用,结果存储在寄存器A中

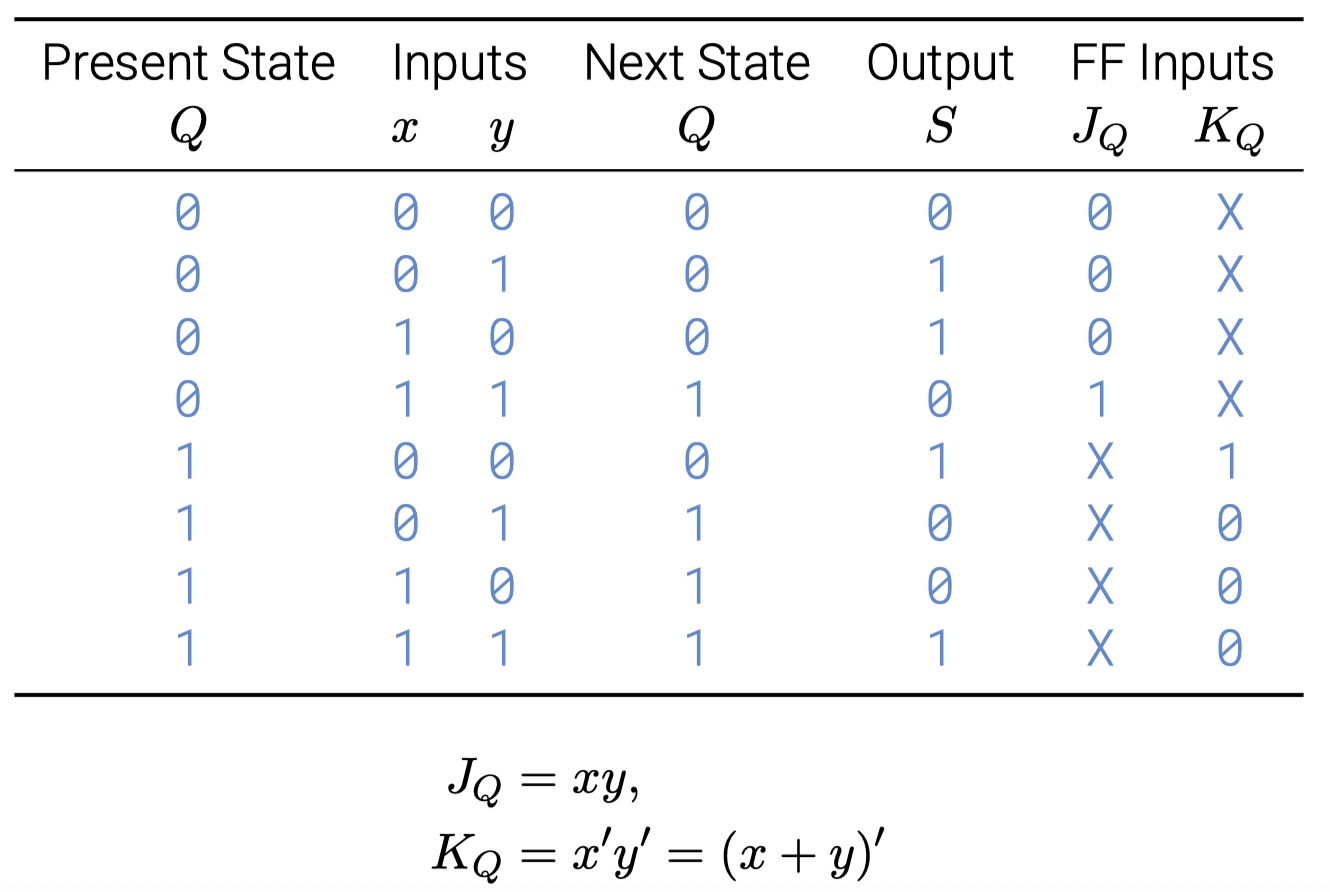

设计一个串行操作 Design a serial operation

我们将利用状态表来重新设计串行加法器。

- 我们假设有两个移位寄存器可以用来存储要串行添加的二进制数字。

- 寄存器的串行输出被指定为x和y。

- 顺序电路有两个输入,x和y,提供一对有效位,一个输出S,生成和位,以及用于存储进位的翻转器Q。

这时候使用D触发器替换JK触发器,电路就会和上面的加法器一样