CS207 Chapter 8

Chapter 8 算术电路 Arithmetic Circuits

算术电路 Arithmetic Circuits

数字设计的一个重要方面是算术电路的设计和实现,这在前面的讲座中没有涉及到。各种信息处理工作是由数字计算机完成的,算术运算是数字计算机的基本功能之一。

加法

两个二进制数字的加法是最基本的算术运算

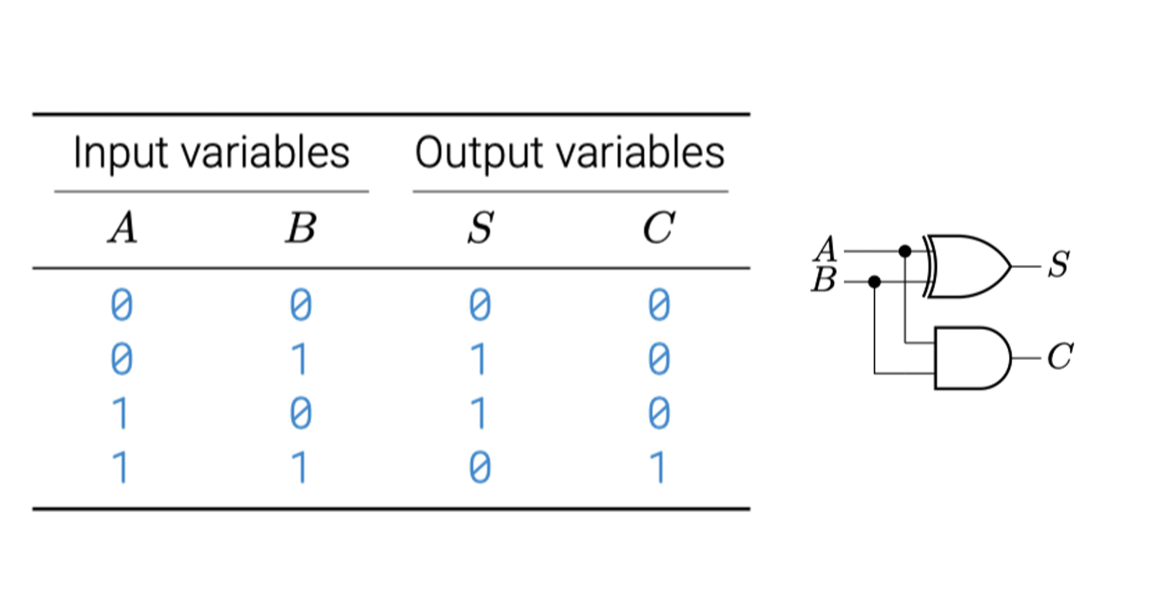

半加器

仅计算两bit的加法,不含进位计算

- 结果 $S = A ⊕ B$

- 进位 $C = AB$

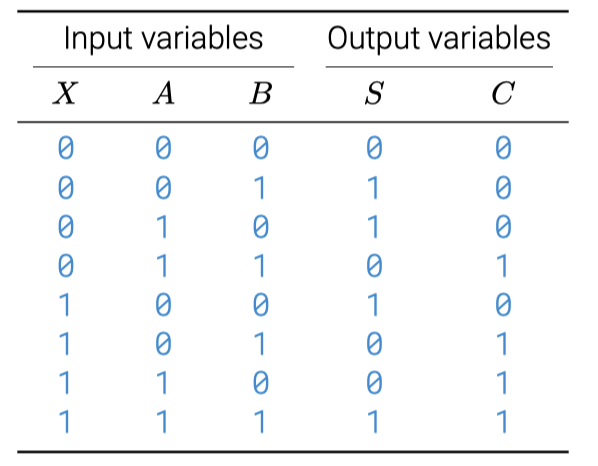

全加器

全加器电路可以进行三个bit的加法,包括两个bit和一个进位,然后产生结果和进位

$S = X’A’B + X’AB’ +XA’B’+ XAB$

$C = AB + BX + AX$

可以通过AND,OR门来实现,同时也可以通过两个半加器和一个or来实现

$S = B ⊕ (X ⊕ A) = B’(XA’+ X’A) + B(XA’+ X’A)’$

$= B’(XA’+ X’A) + B(XA + X’A’) = XA’B’+ X’AB’+ XAB + X’A’B$

$C = B(XA’+ X’A) + XA = XA’B + X’AB + XA$

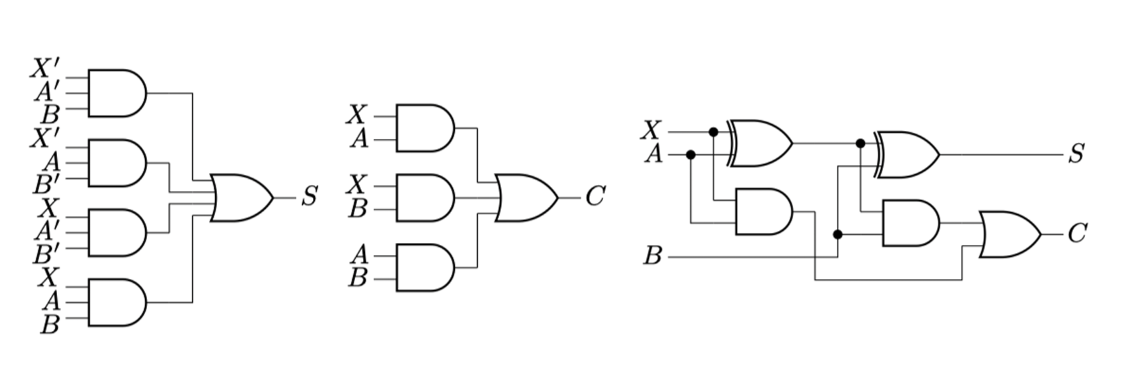

二进制加法器

二进制加法器是一种产生两个二进制数字的算术和的数字电路,n位数的加法需要一个由n个全加器组成的链条,或者由一个半加器和n-1个全加器组成的链条。

减法

减法是数字计算机信息处理任务中算术运算的另一个基本功能

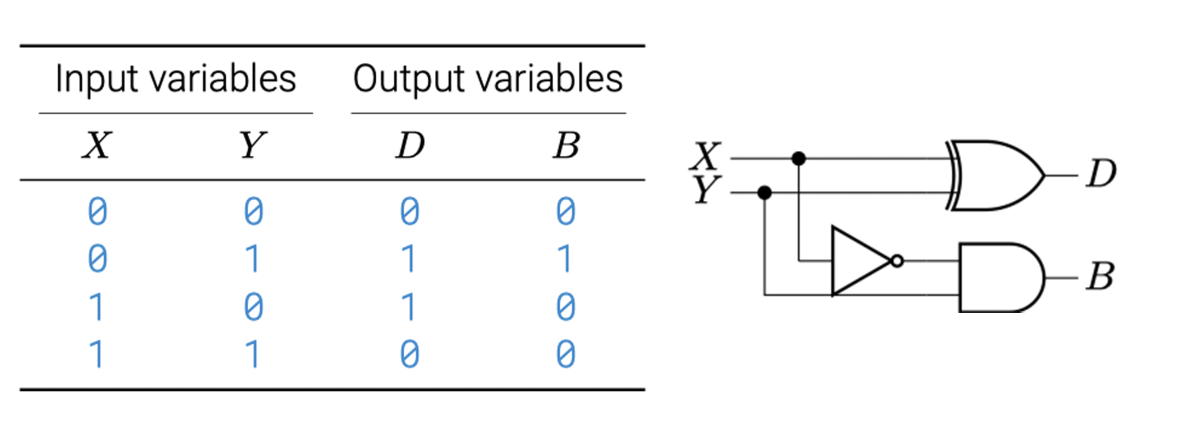

半减器

一个执行两个bit的减法的组合电路被称为半减法器

$D=X⊕Y$

$B = X’Y$

全减器

全加器的组合电路执行三个比特的减法运算–由前一个有效数字的减法运算产生的减数、子数和借数Z,并产生输出差数和借数

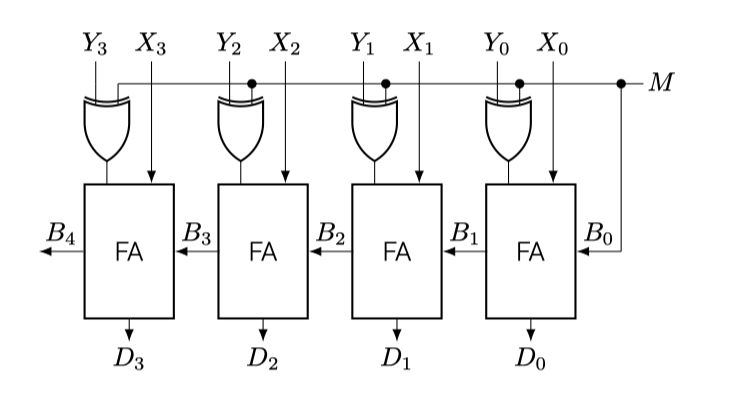

二进制减法器

无符号二进制数的减法可以通过补码的方式最方便地完成。

A-B的减法可以通过取B的补码并将其加到A中来完成。

补码可以通过取反码并在最不重要的一对位上加1来获得。

反码可以用反相器实现,1可以通过输入进位加到总和上。

可以在加法器的Y输入位反相来获得补码,并且在初始位置加一,这样就可以获得减法结果(去掉进位/取补码加负号)

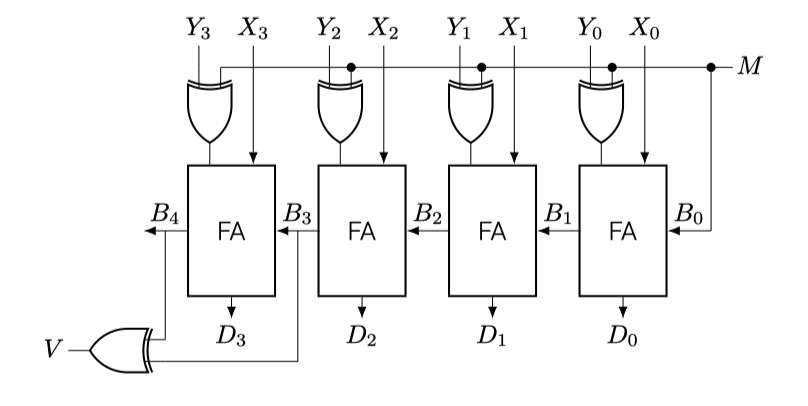

二进制运算器

在设置输入$M$,在$Y$输入变为$Y⊕M$,并且在最小位加法器位置输入$M$。这样就将加减法运算合并为共同一个运算器

溢出

对两个二进制数字相加后的溢出的检测取决于这些数字被认为是有符号还是无符号

当两个无符号的数字相加时,溢出的检测是从最重要的位置的末端进行的

当两个有符号的数字相加时,符号位被视为数字的一部分,末尾进位不表示溢出

如果两个数字都是正数或负数,可能会发生溢出。

- 如果把符号位位置的进位作为结果的符号位,那么这样得到的9位答案将是正确的。但是由于答案不能被容纳在8位之内,我们说发生了溢出。

溢出情况可以通过观察进入符号位的进位和从符号位的出位来检测。如果这两个进位不相等,则发生了溢出。

如果这两个进位被应用于XOR门,当该门的输出等于1时,就可以检测到溢出。

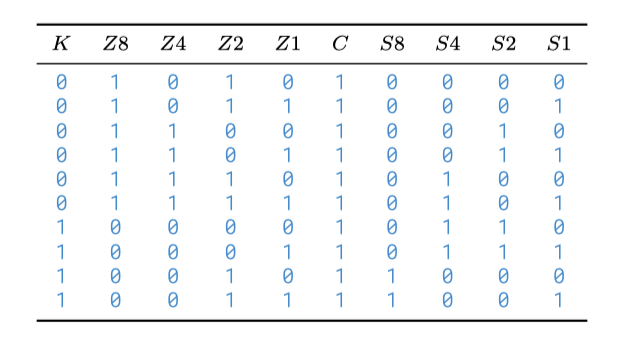

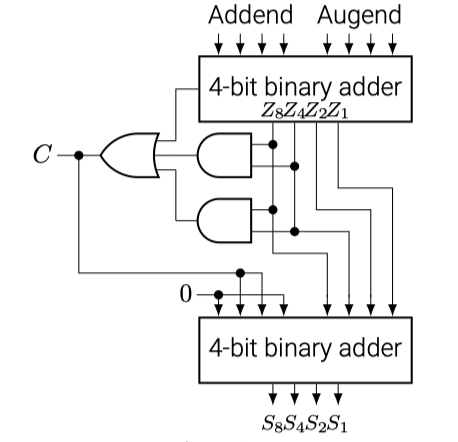

十进制加法器

我们使用BCD来代表十进制,四个bit的二进制加法器能计算BCD码的加法,但是BCD在9之后要加上0110来使其继续合法,需要注意,如下为BCD码合法转化

$K$为进位

合法位$C =K +Z_8Z_4+Z_8Z_2$,不合法的时候可以多一个加法器来加上$0110$

二进制乘法器

略