CS207 Chapter 7

Chapter 7 同步时序逻辑 Synchronous Sequential Logic

同步时序逻辑 Synchronous Sequential Logic

分析时序电路

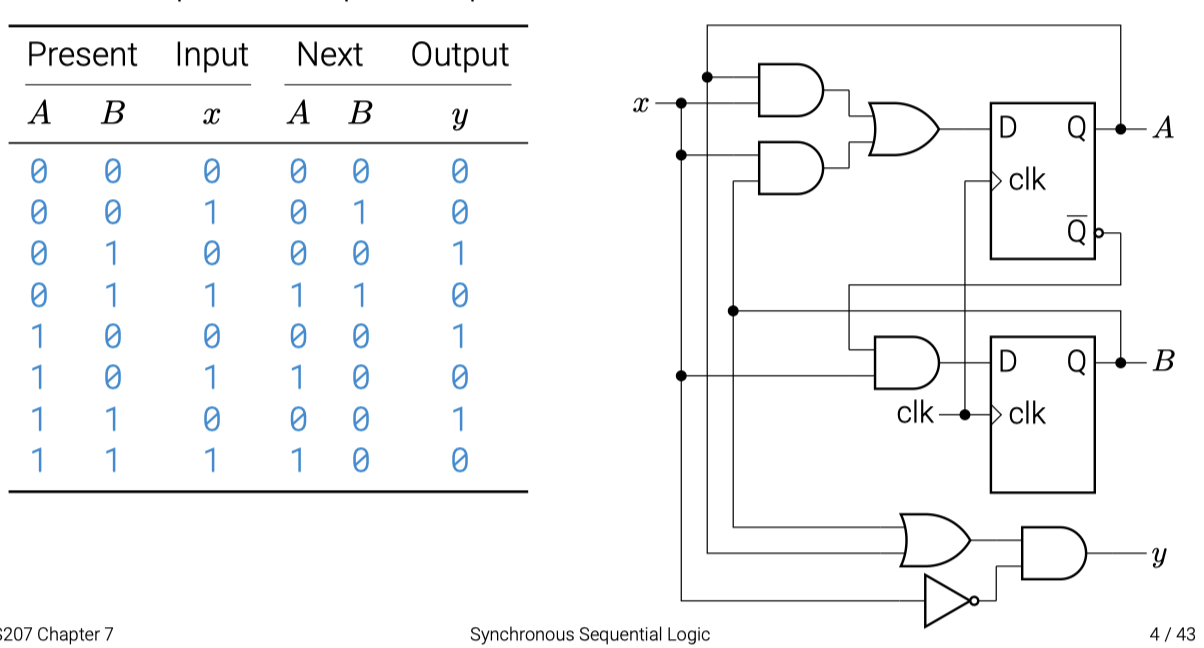

- $A(t + 1) = A(t)x(t) + B(t)x(t)$

- $B(t+1)=A’(t)x(t)$

现在状态t,下一个状态是t+1。然后绘制真值表

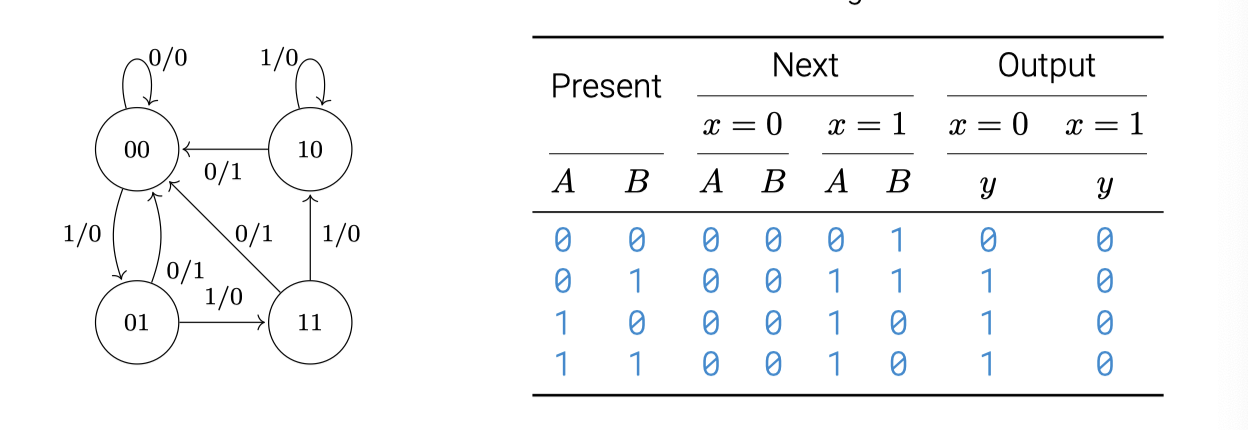

这种真值表很长,可以把x换成两列,接着可以画状态图:

- 电路图→方程式→状态表→状态图

- 状态表更容易从电路图和状态方程中导出

- 状态图给出了状态转换的图解

- 顺序电路的逻辑图由触发器和门组成

- 门之间的互连构成了一个组合电路,可以用布尔表达式进行代数描述

- 组合电路中产生外部输出的部分是由一组称为输出方程的布尔函数代数描述的

- 产生触发器输入的电路部分由一组布尔函数代数描述,称为触发器输入方程(或有时称为激励方程)

一般步骤

- 写出FF输入端函数

- 写出FF的函数

- 代入,并将现有输入转化为FF输入卸载真值表中

- 画出函数图

e.g.:

有限状态机

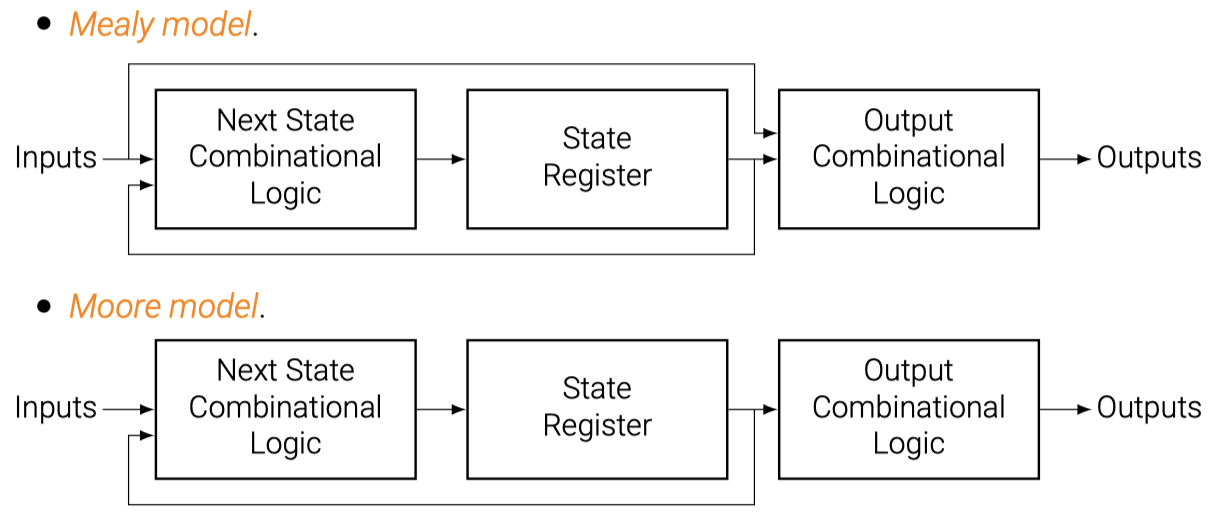

两种模型

状态机化简

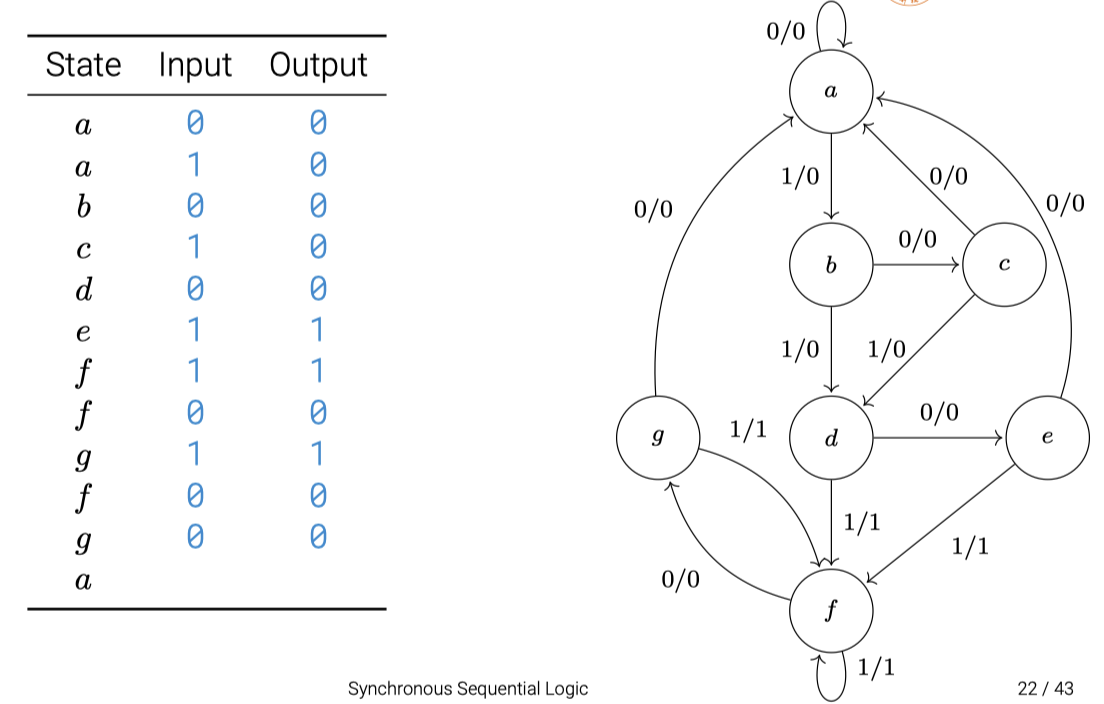

举例,输入$01010110100$

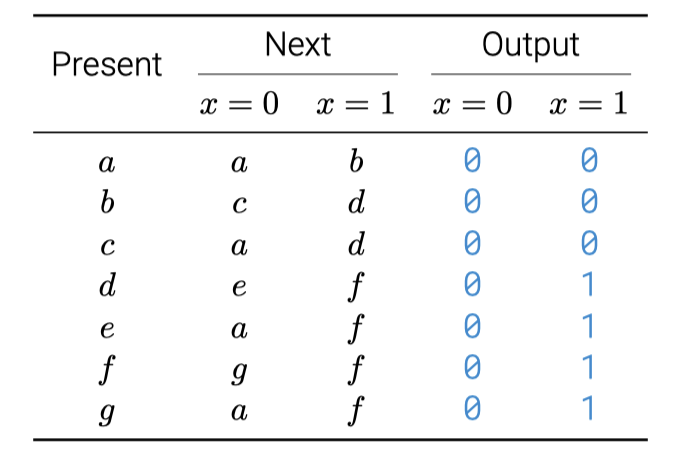

- 首先我们画出状态表

- 然后我们画出目标状态和输出相同组,在上图中e和g是等效的,其中一个可以被另一个替换

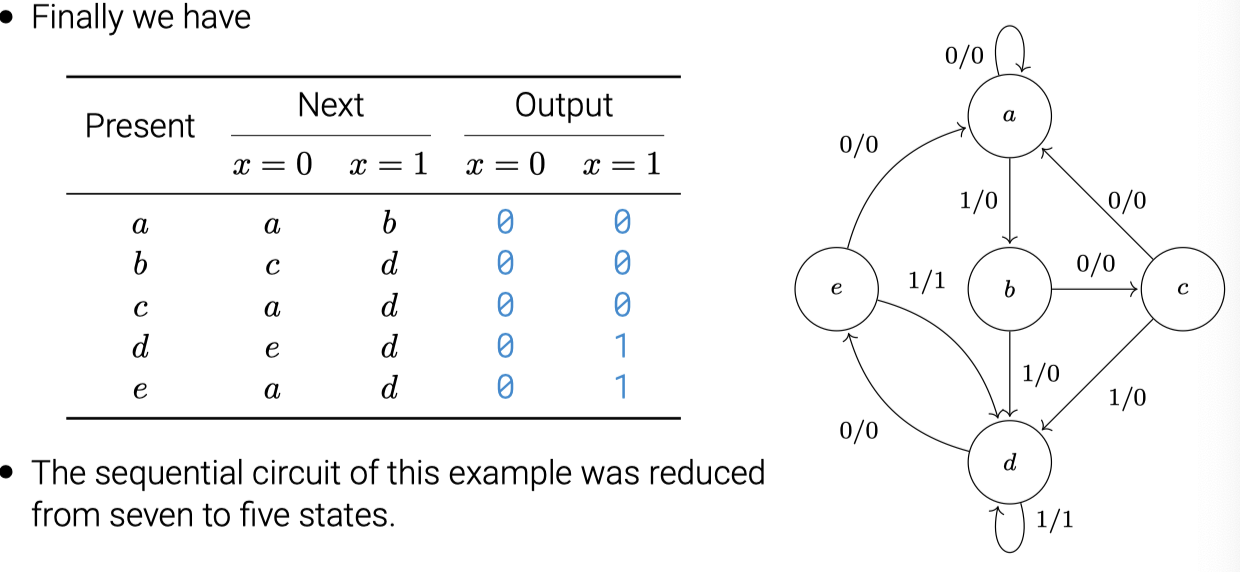

- 重复上述过程,f可以被d替换

- 最终我们的到化简后的状态机

设计状态机

一些注意

- 为了设计一个带有物理元件的顺序电路,有必要为各状态分配唯一的编码二进制值。

- 对于一个有m个状态的电路,编码必须包含n位,其中2 n≥m。

- 在状态还原之前,我们必须为七个状态分配二进制值;剩下的状态是未使用的。如果使用还原后的状态表,只有五个状态需要二进制赋值,而我们还剩下三个未使用的状态。

- 在设计过程中,未使用的状态被当作不关心的条件。由于不关心的条件通常有助于获得更简单的电路,所以有五个状态的电路比有七个状态的电路需要更少的组合门,这是比较有可能的,但并不确定。

- 可以用二进制,格雷码,独热码来设计状态。独热码有更简单的decode

步骤

从字的描述和所需操作的规格,推导出电路的状态图。

如有必要,减少状态的数量。

给状态分配二进制值。

获得二进制编码的状态表。

选择要使用的触发器的类型。

推导出简化的触发器输入方程和输出方程。

绘制逻辑图。

合成FF

用D触发器合成 Synthesis using D flip-flops

用D触发器很简单,目标状态是什么,输入D就是什么,画出真值表然后卡诺图化简即可

激励表

- 使用D型以外的触发器的顺序电路的设计很复杂,因为电路的输入方程必须间接地从状态表中得到。当采用D型触发器时,输入方程可以直接从下一个状态中获得。

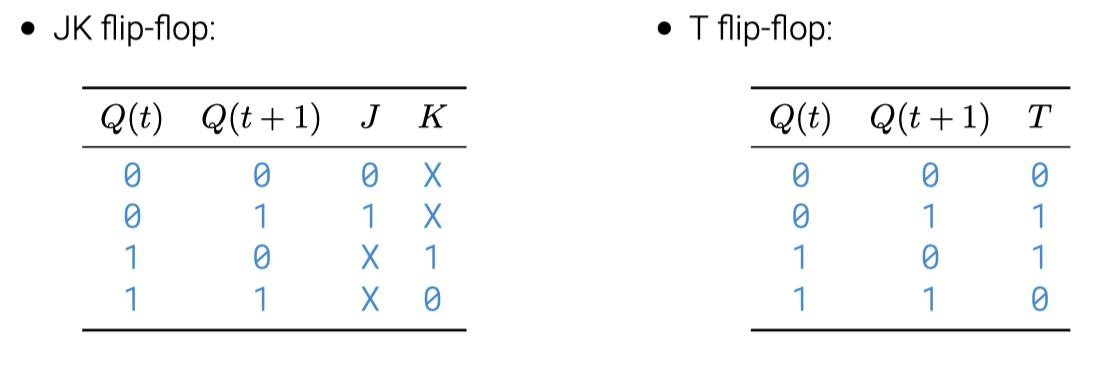

- 而JK和T型触发器则不然。为了确定这些触发器的输入方程,有必要推导出状态表和输入方程之间的函数关系。

- 在设计过程中,我们通常知道从当前状态到下一个状态的转换,并希望找到能引起所需转换的触发器输入条件。

- 出于这个原因,我们需要一个表格,列出特定状态变化所需的输入:激励表

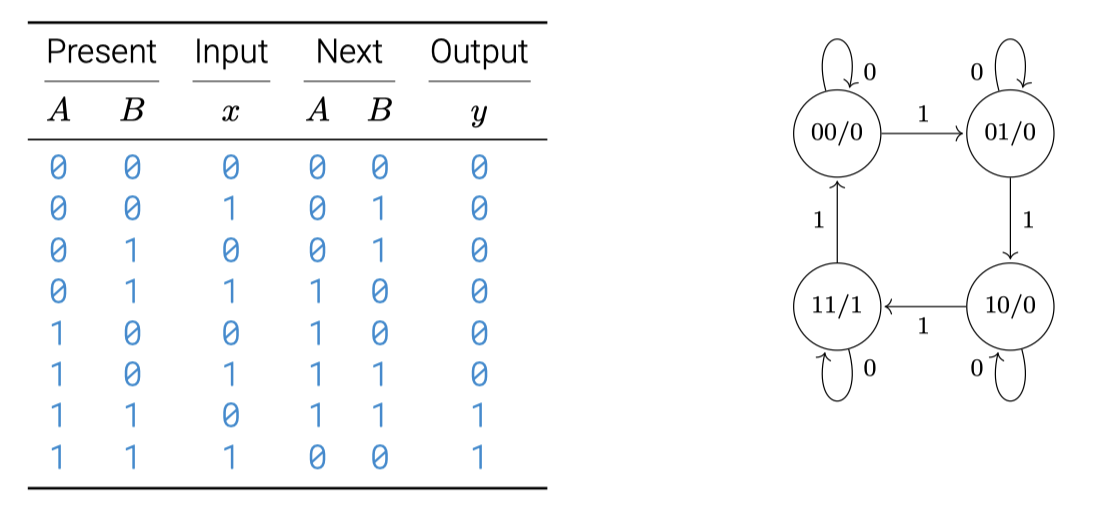

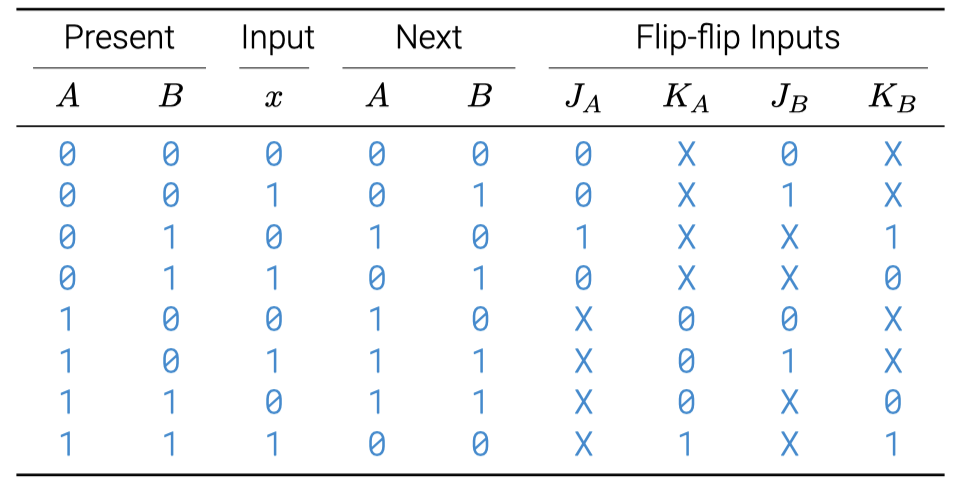

用JK触发器合成 Synthesis using JK flip-flops

这时候根据A,B的变化找到对应的输入J K

再用真值表化简出$J_AK_AJ_BK_B$的函数,再绘制电路图即可

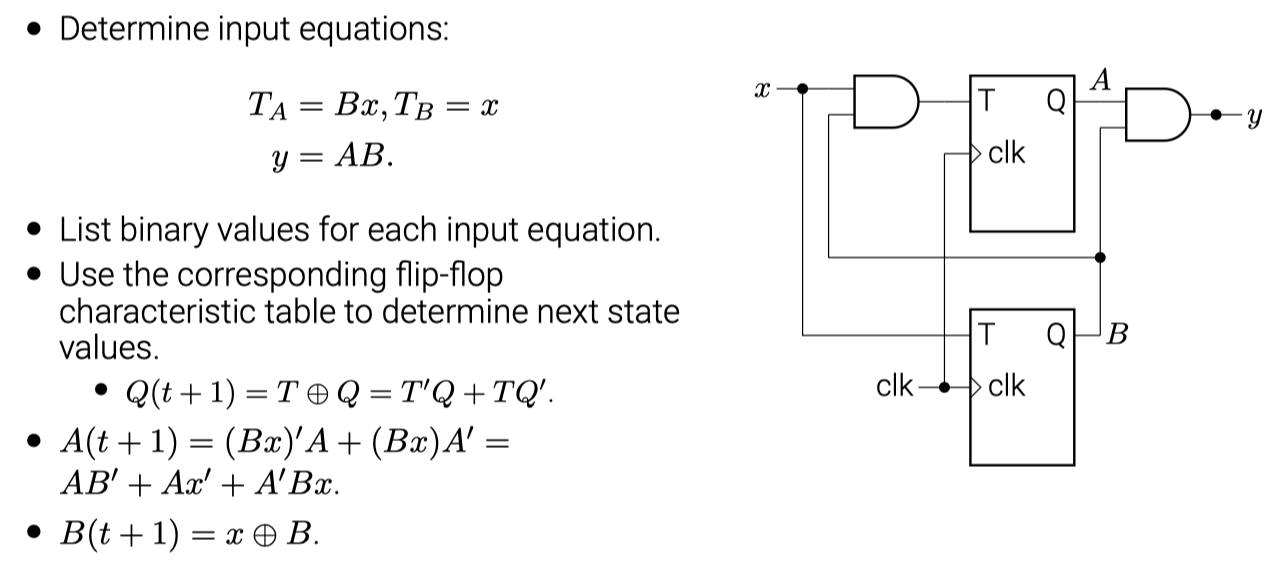

用T触发器合成 Synthesis using T flip-flops

TFF的合成就简单很多,只要下一个状态有变化,T就是1,没有变化就是0,再用卡诺图化简即可