CS207 Chapter 6

Chapter 6 锁存器和触发器 Latches and Flip-flops

锁存器和触发器 Latches and Flip-flops

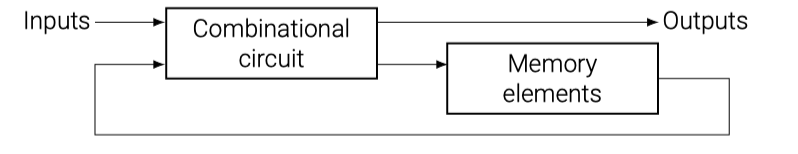

其在任何瞬间的输出都取决于现在的输入和过去的输出的逻辑电路被称为顺序电路。

- 一个组合电路,但有

- 记忆元素连接在反馈路径中。

- 输出不仅是输入的二进制函数,也是电路的当前状态。

- 记忆元件是一种媒介,其中的一位信息(0或1)可以被存储或保留到必要时,此后其内容可以被一个新的值所取代。

顺序电路大致分为两大类,称为同步或有时钟的顺序电路,以及异步或无时钟的顺序电路,取决于其信号的时间。一个序列电路的行为可以通过对其信号在离散时间段的了解来定义,被称为同步序列电路,一个序列电路的行为取决于输入信号的变化顺序,被称为异步序列电路。

触发器Flip-Flop

Flip-Flop是一种记忆原件,仅存储1bit的数据,只在一个时钟脉冲内有电位变化,时钟不激活不变化

它只能有两个状态,要么是1状态,要么是0状态。

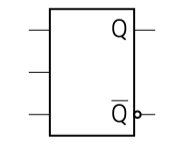

- 触发器的一般框图表示如下,它有一个或多个输入和两个输出,这两个输出是相互补充的。

- 通常,Q的状态被称为触发器的状态,而Q′的状态被称为触发器的互补状态。

注意

对于锁存器和触发器这两个术语的使用,一直存在着相当大的混淆。

- 触发器是一种在时钟信号发生变化时改变其状态的设备。

- 异步锁存器持续监测输入信号,在输入信号发生变化时改变其状态。

- 同步锁存器持续监测输入信号,但只有在控制信号激活时才能改变其状态。

锁存器 Latches

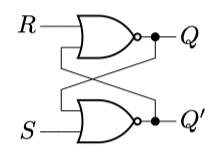

SR Latches

通过交叉耦合一对NOR门,我们有了第一个锁存器。SR锁存器

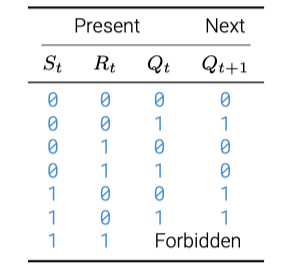

- 设置和复位的输入端分别被标为S和R,SR锁存器的状态表如下所示

- 在k-map中$Q_{t+1}=S+R’Q$

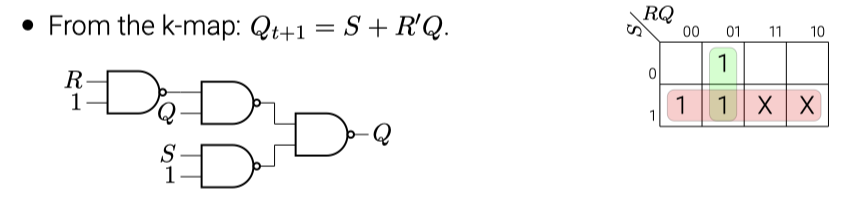

Controlled SR Latches

- SR锁存器的可控性可以由一个额外的信号G控制。

如果G=0,第一级NAND门的输出总是1,禁用第二级门的任何变化。

如果G从0过渡到1,第一级NAND门被启用,使锁存器处于激活状态。

- 但是SR锁存器若S和R都是1时输出不可预知

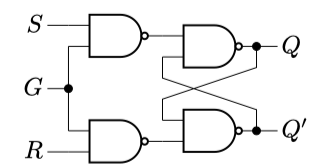

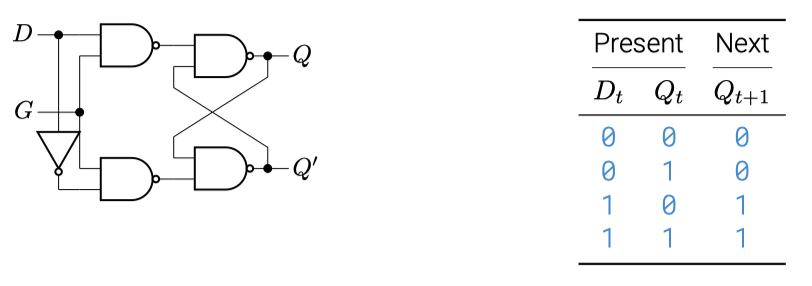

Controlled D Latch

- D锁存器被设计用来处理这个问题,D锁存器也叫透明锁存器,D代表数据,确保前面的S和R永远不会同时等于1

- 受控D型锁存器的优点是只需要一个数据输入,没有必须要避免的输入条件

- 当enable被断言时,数据输入被转移到Q输出。输出跟随输入

- 当使能被解除时,信息被储存

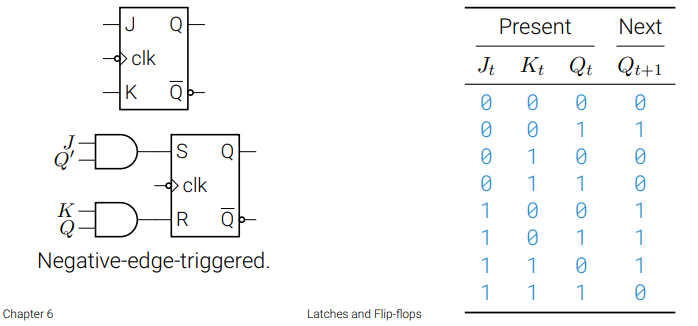

JK 触发器 JK flip-flop

锁存器电路由于其透明性而不适合在同步顺序电路中运行。触发器被用作基本的存储元件,它只对clk输入激活时的变化作出反应,一个典型的例子被称为JK触发器(JKFF)1 0 置1, 0 1置0, 1 1 反转, 00不变

主-从JK FF

主控器的时钟是正常的,而从属器的时钟是反转的。当时钟变为0时,从机被激活以反映来自主机的数据。主站的数据到输出。但是,主锁存器被禁用:输入的进一步变化将不会被反映出来。可以继续添加控制Clear和Preset来覆盖JK输入,Cl Pr 1 0时 清除主从的Q为0,0 1 时 Q预设为1。同时激活时存储器锁住不再变化,0 0 时对外界可做出相应

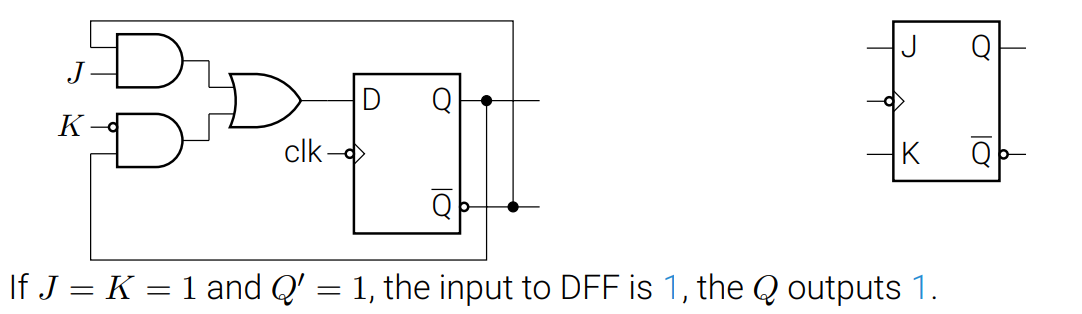

D flip-flop

如latch一样,将K输入为J的逆。

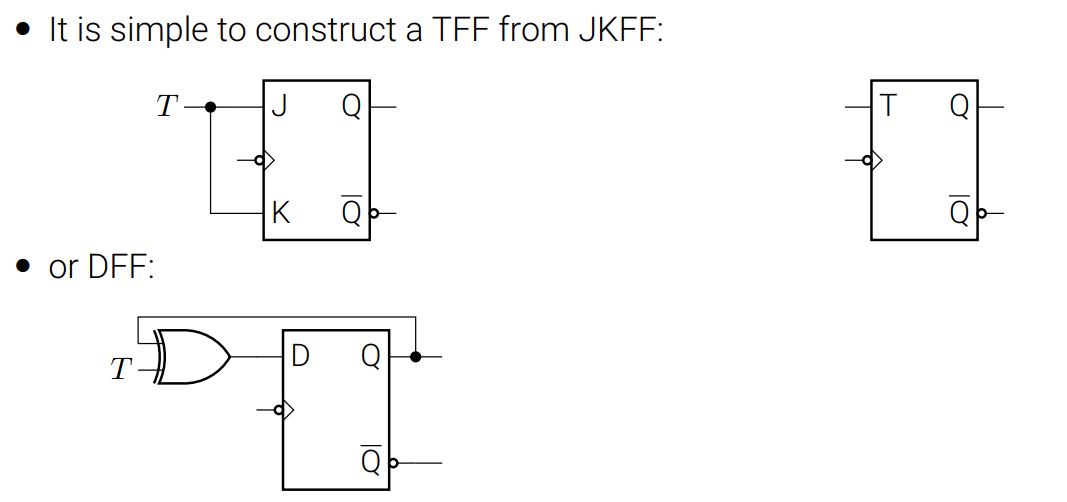

T flip-flop

最后,当输入T=1的时钟信号时,一个T触发器会切换状态,构造下面有

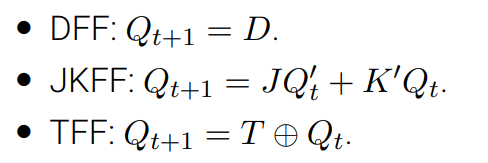

FF间的转换

- JKFF => DFF:链接K为J的反向

- DFF => JKFF:如图

- JKFF & DFF => TFF:

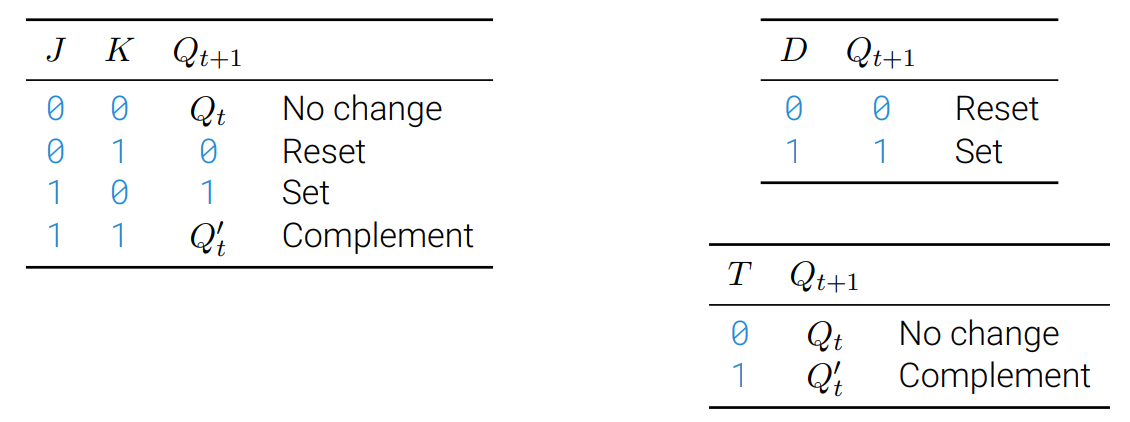

特性表 Characteristic table

- 特性表通过描述一个触发器的逻辑属性以表格的形式描述其操作。

特性方程 Characteristic equation