CS207 Chapter 5

Chapter 5 组合逻辑电路 Combinational logic

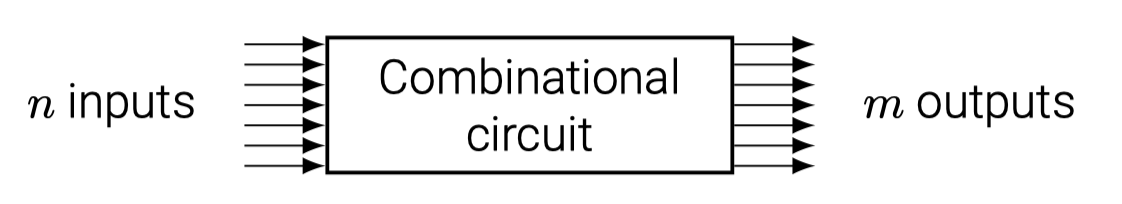

组合逻辑电路 Combinational logic

逻辑电路分为组合逻辑和时序逻辑,组合逻辑电路的输出取决于输入的组合,可以实现一个布尔函数的运算,对输入变量的值和组合敏感并且输出一组值。

输入共有$2^n$个组合,可以用真值表表示,m个输出根据输入来决定

Multiplexer 多路复用器

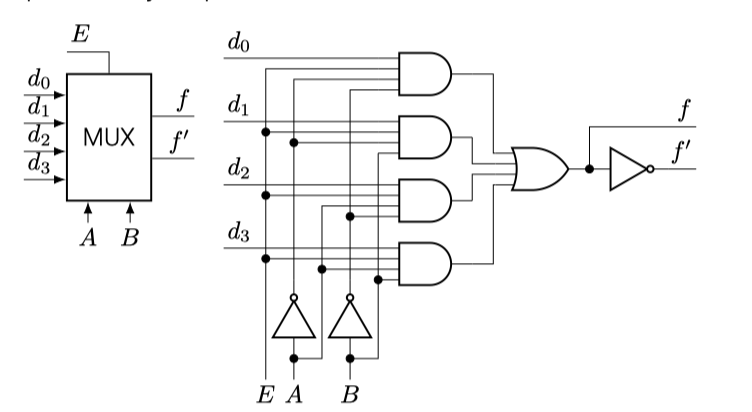

多路复用器通过n个输入(通常为2,4,8,16)以及一个开关E以及选择输入来决定输出哪一个输入。

数字系统内的数据通常以并行形式处理,以提高运行速度。

如果系统的输出必须在一个相对较长的距离内传输,那么将进行并行到串行的转换。

例如一个8位字在数据输入端以并行方式呈现

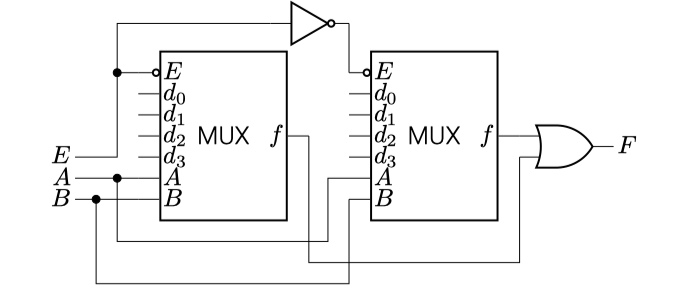

用作生成布尔函数

对于一个4对1的MUX,其特征方程为 $f = A’B’d_0 + A’Bd_1 + AB’d_2 + ABd_3 $

- A和B是布尔变量,应用在选择输入端,可以从任何n个变量的布尔函数中分解出来。

- 剩下的n-2个变量,被称为残差变量,可以形成残差函数,然后可以应用于数据输入。

- 例如:$f(A,B,C)=∑(0,1,3,4,7)$

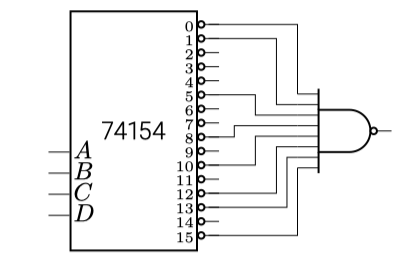

Decoder 解码器

- 可以看出,解码器的逻辑图与解复用器的逻辑图是相同的,只要数据线被用来启用解码器。

- 解码器也可以被看作是一个SOP发生器。每个输出都产生一个minterm。

如下为$f(A, B, C, D) = ∑ (0, 1, 5, 8, 10, 12, 13, 15)$

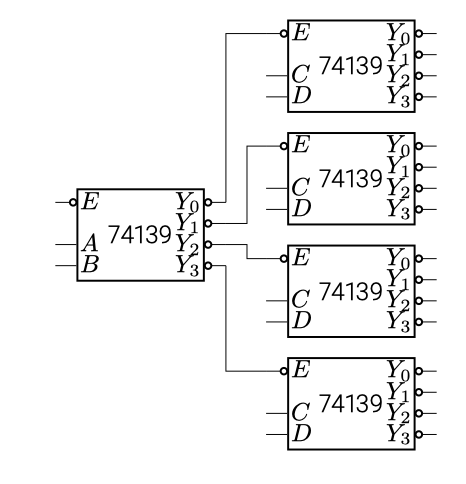

解码器网络

- 当需要一个大型的解码网络时,它不能在一个MSI封装中实现。

- 主要是由于需要大量的引脚。

- 解码范围可以通过解码器芯片的互连来扩展。两种方案。

树状解码 Tree decoding

巧合解码 Coincident decoding

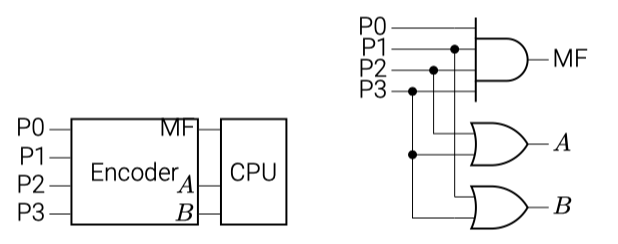

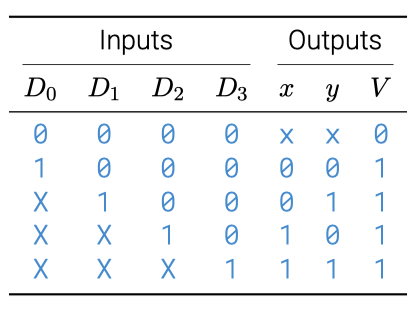

Encoder 编码器

编码器就是解码器的反向操作,一般用于CPU master flag,将输入的独热玛转换为二进制数字

- 编码器被设计为在任何给定的瞬间识别一个,而且只有一个外围设备。

- 在实践中,没有什么可以阻止两个或更多的外设同时请求服务。

- 为了处理这种情况,可以给外设标志附加一个优先级系统。

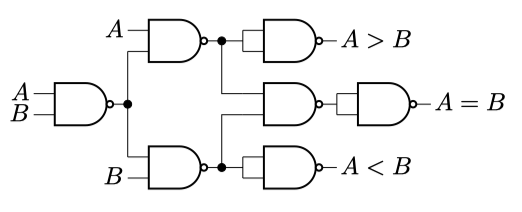

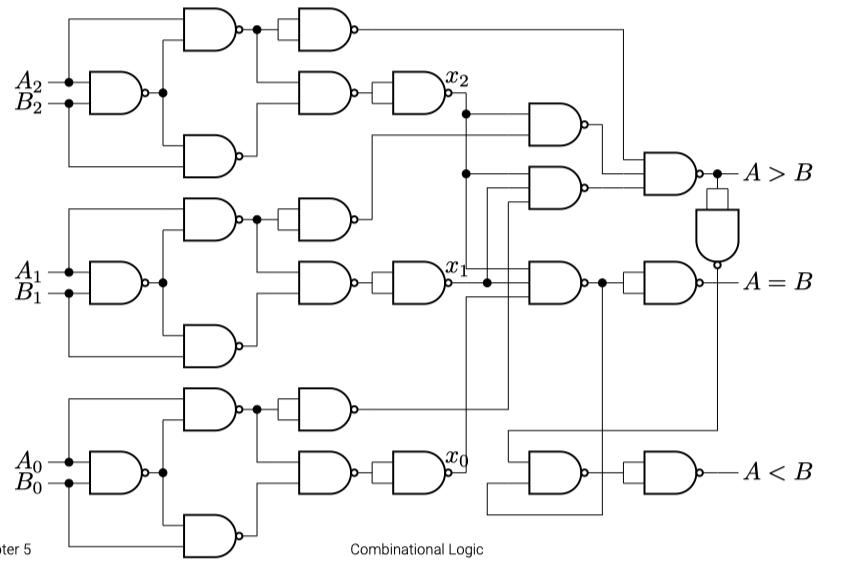

Digital Comparator 比较器

• 比较器的通常问题是两个多位数字的比较

such as $A = A_2A_1A_0 $and $B = B_2 B_1 B_0$

• 从最有意义的位(最大)开始到最小的位

A = B 如果所有的位数都相等: $A_i = B_i$

$x_i =A_i B_i +A_i’B_i’$

A = B if $x_2 x_1 x_0 = 1$

A > B if $A_2 B_2’+ x_2 A_1 B_1’+ x_2 x_1 A_0 B_0’= 1$

A < B if $A_2’B_2 + x_2 A_1’B_1 + x_2 x_1 A_0’B_0 = 1$

单bit比较器:

3 bit比较器:

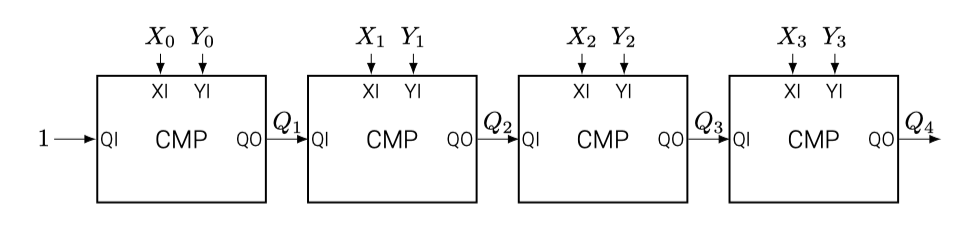

迭代组合电路

- 一般结构:相同功能的n个相同的模块,对于可以通过迭代算法解决的问题。

- 将$C_0$设为其初始值,并将i设为0。

- 当i<n时,重复。

- 用$C_i$和$D_i$来确定$O_i$和$C_{i+1}$的值。

- 增加i

- 初级输入/输出和级联输入/输出。

例如,使用迭代组合电路比大小,模块为1bit比较器:

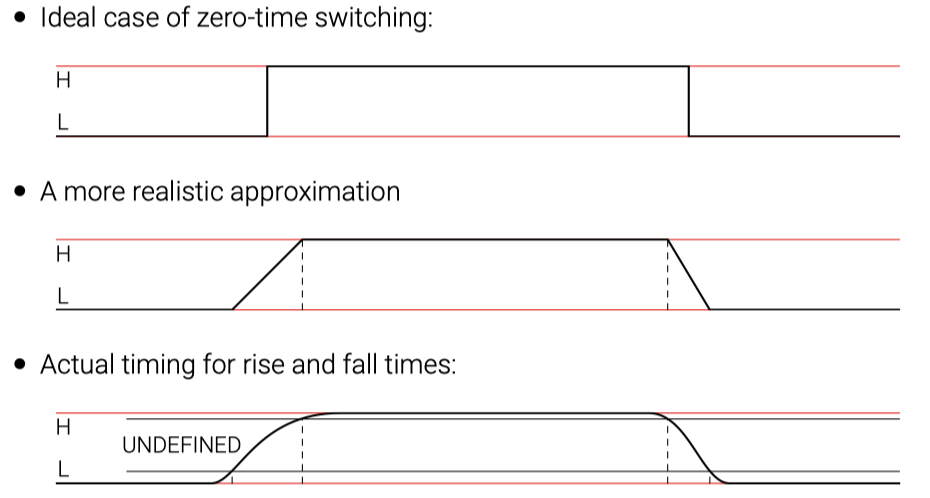

门延迟

在电位变化过程中有延迟,中间部分不会被定义为高/低电位

- 忽略延迟的组合电路的分析只能预测其稳态行为。

- 假设相对于电路中的电子元件的延迟而言,输入已经稳定了很长时间,则预测电路的输出为其输入的函数。

- 由于电路的延迟,组合逻辑电路的瞬态行为可能与稳态分析的预测不同。

- 时序危险:当稳态分析预测输出不应改变时,电路的输出可能产生一个短脉冲(突波glitch)

- 一个门有可测量的响应时间$t_{pLH}$和$t_{pHL}$。每个门大约10ns。

- 通过传输门的延迟可以累加起来,并引入时间危险。

- $t_{pLH}$= 低到高,$t_{pHL}$= 高到低的传播时间

- static-1危险是一个短暂的0突变,当输入改变时,我们期望(根据逻辑定理)输出保持恒定的1

- static-0危险是一个短暂的1突变,当我们期望输出保持恒定的0